Generate and Synthesize HDL Code for Resonant LLC Converter Using Fixed-Point Data Type

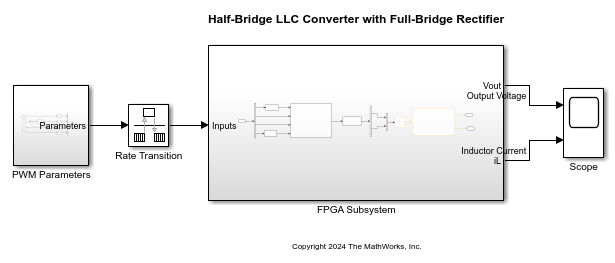

This example shows how to model a resonant LLC converter by using Simscape™ switches with fixed-point data type. You can generate HDL code and synthesize the results for real-time simulation.

Set Up Synthesis Tool Path

To synthesize the generated HDL code, before you use HDL Coder™ to generate code, set up your synthesis tool path. For example, if your synthesis tool is Xilinx® Vivado®, install the latest version of Xilinx Vivado as shown in HDL Language Support and Supported Third-Party Tools and Hardware.

Then, set the tool path to the installed Xilinx Vivado executable by using the hdlsetuptoolpath function:

hdlsetuptoolpath('ToolName','Xilinx Vivado','ToolPath','C:\Xilinx\Vivado\2022.1\bin\vivado.bat')

Resonant LLC Converter with Fixed-Point Data Type

This example shows the topology of a half-bridge resonant LLC converter with a full-bridge rectifier designed to run at a sample time of 20 ns. A resonant LLC converter is a DC-DC converter that uses a resonant tank circuit to achieve high efficiency and improved performance. It is widely used in applications requiring high efficiency and reliable operation, such as power supplies for servers, telecommunication equipment, and consumer electronics. The resonant LLC converter minimizes switching loss by achieving zero-voltage switching (ZVS). It can effectively regulate the output voltage across a wide range of load conditions. This is achieved through the unique design of the LLC resonant tank, which consists of two inductors (L) and one capacitor (C). The resonant frequency of this tank can be adjusted to ensure that the converter operates efficiently even at light loads.

In the resonant LLC converter represented in the model, the converter switches are triggered by a 100 kHz pulse with a duty cycle, D, of 0.5. In this topology, the switching bridge generates a square waveform to excite the LLC resonant tank. This, in turn, generates a resonant sinusoidal voltage that is stepped up or down by the transformer and then rectified by the rectifier circuit. The output capacitor filters the rectified voltage and outputs a DC voltage.

The data type precision for the model is set to fixed-point with a 36-bit word length. Using fixed-point precision determines the dynamic range of state-space matrices, and computes the appropriate fraction lengths and full-precision integer rounding modes by using the specified word length. This reduces resource utilization and improves FPGA sampling frequency.

Open the model at the MATLAB® command prompt.

open_system("sschdlexResonantLLCConverterExample")

The configurations inside the FPGA Subsystem block run on an FPGA board and the components that are outside the FPGA Subsystem block run on a CPU in real time. Open the FPGA Subsystem block that contains Simscape blocks.

open_system("sschdlexResonantLLCConverterExample/FPGA Subsystem")

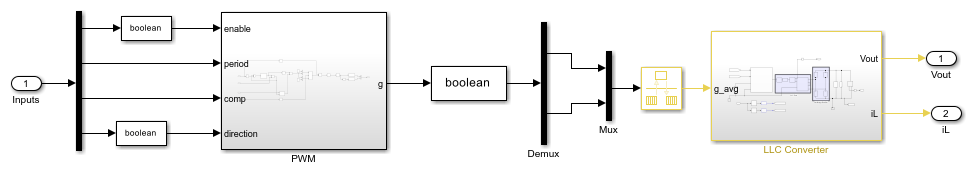

The FPGA Subsystem block contains a pulse generator (PWM subsystem) and an LLC converter circuit (LLC Converter subsystem). You can generate VHDL code for the blocks inside this FPGA Subsystem block.

Run Desktop Simulation

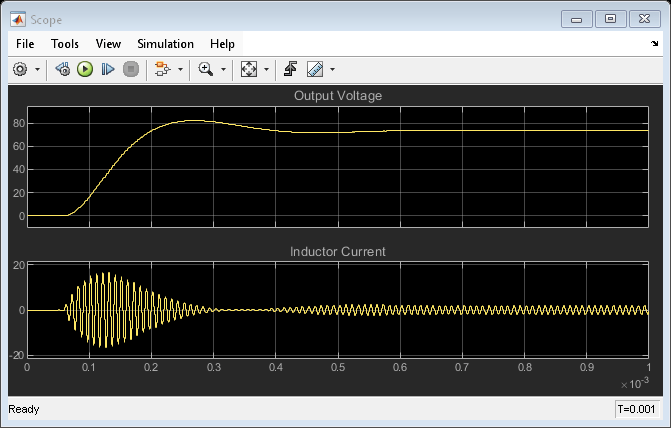

The DC input voltage to the LLC Converter circuit is 340 V. The input signals (that include a PWM frequency and duty cycle) are provided to generate the gate pulses with a frequency of 100 kHz with 50% duty ratio in the FPGA Subsystem block of the model with the sample time of the Simscape model set to 20 ns. The scope provides the output voltage and inductor current waveforms.

To see the waveforms, simulate the model.

sim("sschdlexResonantLLCConverterExample"); open_system("sschdlexResonantLLCConverterExample/Scope")

Generate HDL Code and Synthesize the Results

To generate the HDL code, first generate an HDL implementation model from the Simscape model by using the Simscape HDL Workflow Advisor. For details, see Generate Optimized HDL Implementation Model from Simscape.

After the task passes in the Advisor, you see a link to the generated HDL implementation model. You generate HDL code for this generated HDL implementation model and synthesize the HDL code. For details about the HDL code generation and synthesis of code, see Generate FPGA Bitstream for Two-Phase DC-DC Converter with Tunable Run-Time Parameters.

You can select the data type precision in the Generate implementation model task pane of the Simscape HDL Workflow Advisor.

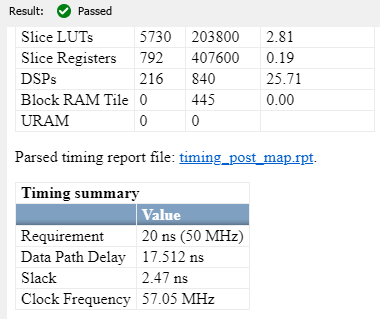

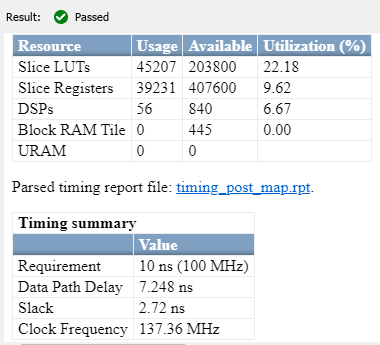

The resonant LLC converter model is synthesized for two cases:

Case1 — Data type precision is set to

Singleand an equivalent state-space model is generated with a Validation logic tolerance of0.25. Target Frequency is set to100 MHz.

Case2 — Data type precision is set to

Fixed-pointwith Fixed-point word length set to36-bit. The equivalent state-space model is generated with a Validation logic tolerance of0.25. Target Frequency is set to50 MHz.