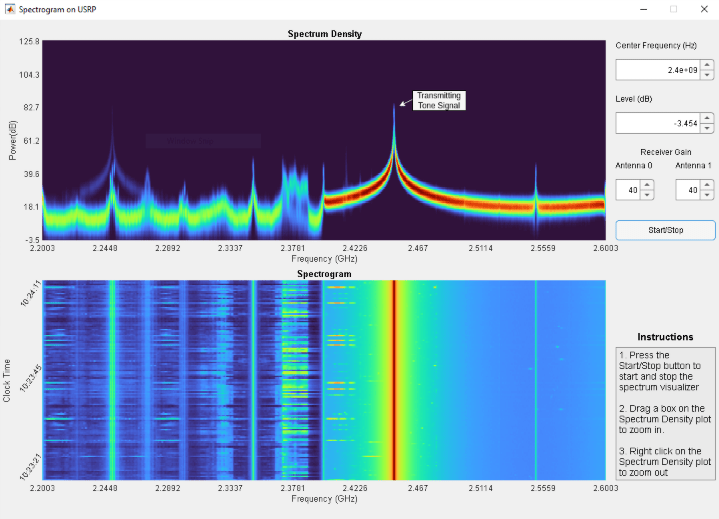

Target NI USRP Radios

Deploy custom software-defined radio (SDR) algorithms on the FPGA of an NI USRP radio using a Simulink® and HDL Coder™ workflow. Run and verify your design using MATLAB® objects and functions.

Objects

usrp | Control NI USRP radio device (Since R2024a) |

fpga | Access DUT on the FPGA of an NI USRP radio device (Since R2024a) |

hdlcoder.DUTPort | DUT port object array that represents DUT ports on custom FPGA image (Since R2024a) |

Functions

Topics

- Supported Radio Devices

Determine which NI USRP radios you can target with Wireless Testbench™.

- System Requirements

Determine the host system requirements for targeting NI USRP radios.

- Installation for Targeting NI USRP Radios

Install and configure additional support packages and third-party tools.

- Target NI USRP Radios Workflow

Prototype and deploy SDR algorithms on the FPGA of an NI USRP radio.

- STEP 1: Verify Radio Connection

- STEP 2: Set Up Third-Party Tools

- STEP 3: Prepare Hardware Model for Deployment

- STEP 4: Generate HDL Code

- STEP 5: Generate Bitstream and Program FPGA

- STEP 6: Run and Verify Hardware Implementation

- Reduce Resource Utilization and Achieve Timing Closure

How to and leverage optimization and clocking features to reduce resources and achieve timing closure. (Since R2026a)

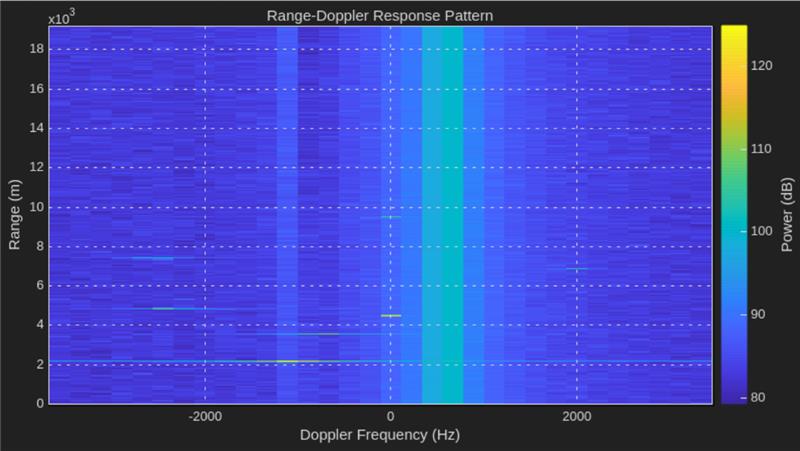

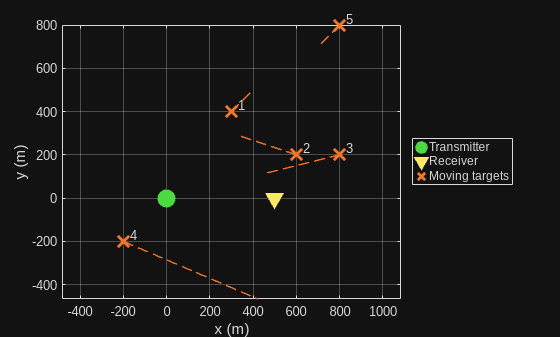

- Radar Target Emulation Applications Overview

Learn about the relationships between the family of radar target emulation examples. (Since R2026a)

Troubleshooting

Resolve Issues with Generating and Loading Bitstreams

Troubleshoot issues encountered when generating and loading bitstreams. (Since R2026a)