HDL Code Generation, Verification, and Deployment

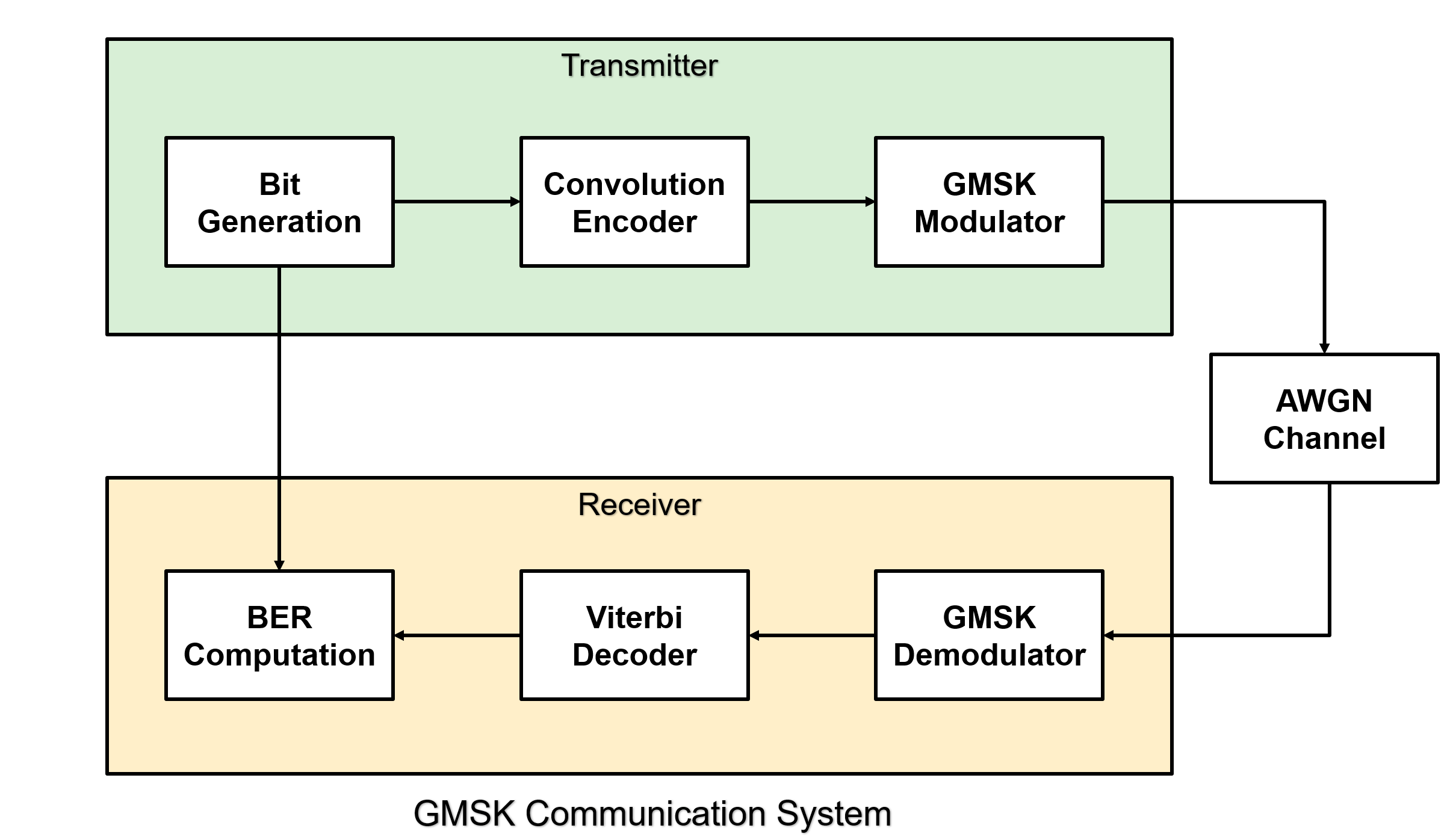

After simulating your designs using Wireless HDL Toolbox™ blocks, the next steps are to generate HDL code, verify the generated code, and deploy to hardware. To generate HDL code from designs that use the hardware-friendly Wireless HDL Toolbox blocks, you must have an HDL Coder license. HDL Coder also enables you to generate scripts and test benches for use with third-party HDL simulators.

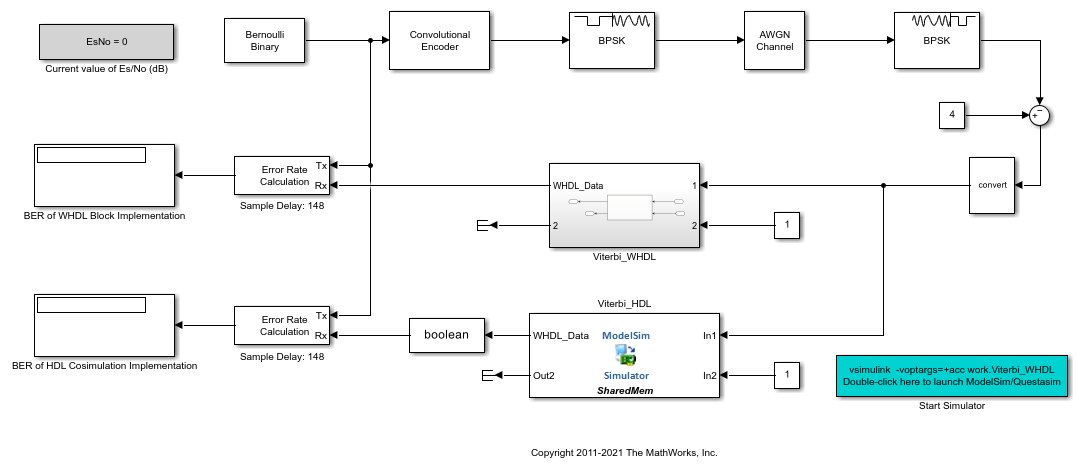

If you have an HDL Verifier license, you can use the FPGA-in-the-loop (FIL) feature to prototype your HDL design on an FPGA board. The FIL blocks provide efficiency improvements for streaming data across the interface between Simulink® and the FPGA board. HDL Verifier also enables you to cosimulate a Simulink model with an HDL design running in a third-party simulator.

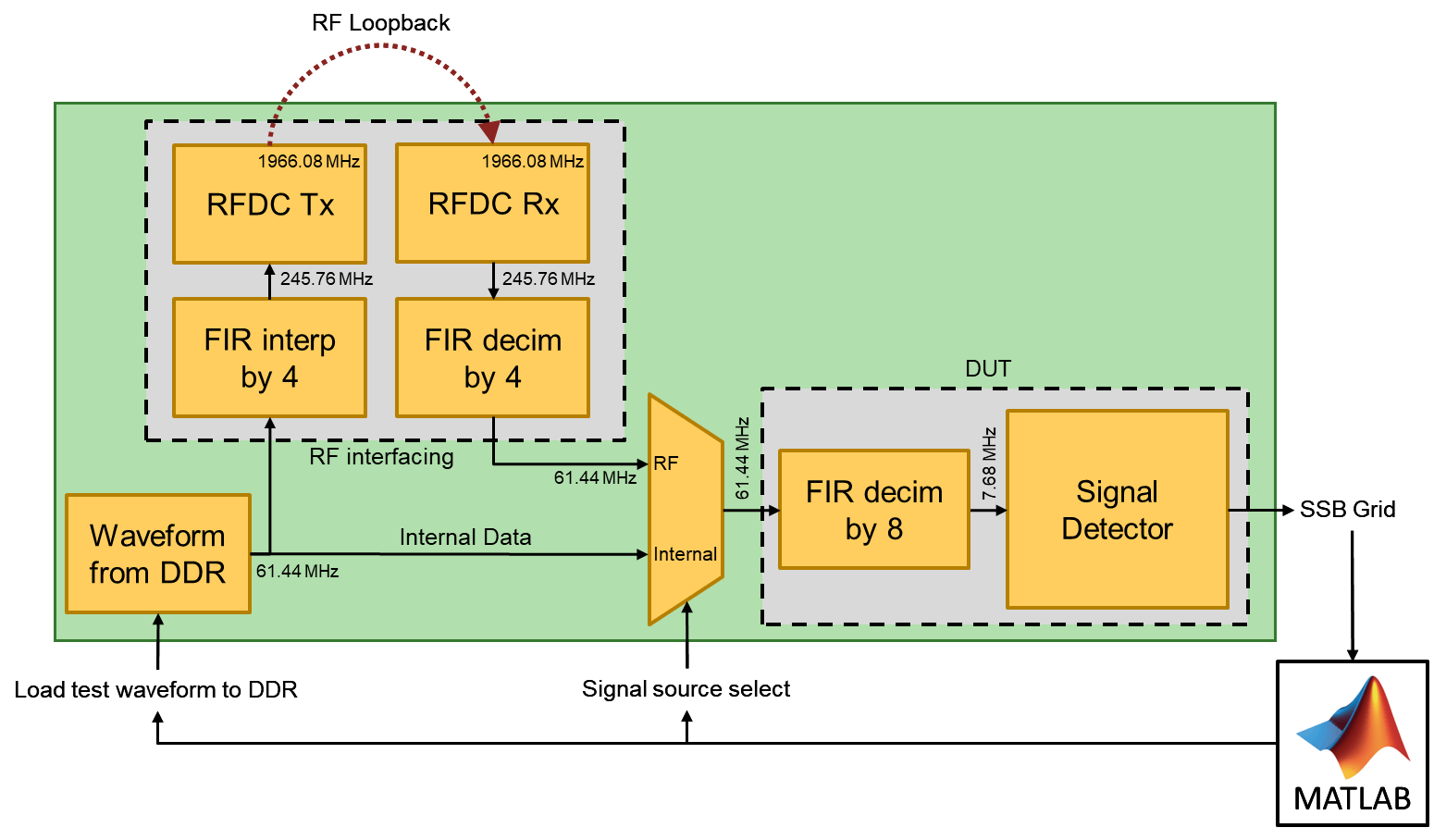

To design, prototype, and verify practical wireless communications systems on hardware, download hardware support packages such as SoC Blockset™ Support Package for AMD FPGA and SoC Devices.

Blocks

| FIL Frame To Samples | Convert frame-based data to sample stream for FPGA-in-the-loop |

| FIL Samples To Frame | Convert sample stream from FPGA-in-the-loop to frame-based data |

Topics

- HDL Code Generation Support

Find supported blocks, and implement streaming interface in HDL.

- Generate HDL Code

Generate HDL code from Simulink subsystems.

- FPGA-in-the-Loop

Real-time design verification of communications systems with FPGAs.

- Prototype Wireless Communications Algorithms on Hardware

Prototype Wireless HDL Toolbox designs on AMD® Zynq®-based boards using hardware support packages.

Related Information

- HDL Coder

- HDL Verifier

- AMD FPGA and SoC Devices (SoC Blockset)