System on Chip (SoC)

Create SoC, MCU, or application-specific SoC Simulink® models of an application. Use preconfigured model templates or follow the SoC model guidelines. SoC Blockset™ model templates provide design patterns and implement best practices for creating an SoC model. The suggested workflow shows the process to combine processor software, user-specified programmable logic, shared memory systems, and on-chip peripherals to create an SoC model of an application. Use analysis functions and tools to estimate the resources that application uses. Compare different architectures to understand design tradeoffs in partitioning between processor software and programmable logic.

The blockset exports reference designs for SoCs, MCUs, ASICs, and FPGAs using Xilinx®, Intel®, and Texas Instruments® design tools. Automatically generate hardware and software code, and then execute the application on an SoC device by using the SoC Builder tool. Code generation requires the HDL Coder™ product, Embedded Coder® product, or both.

Apps

| Embedded Linux Explorer | Connect to hardware, monitor resources, and control applications running embedded Linux (Since R2023a) |

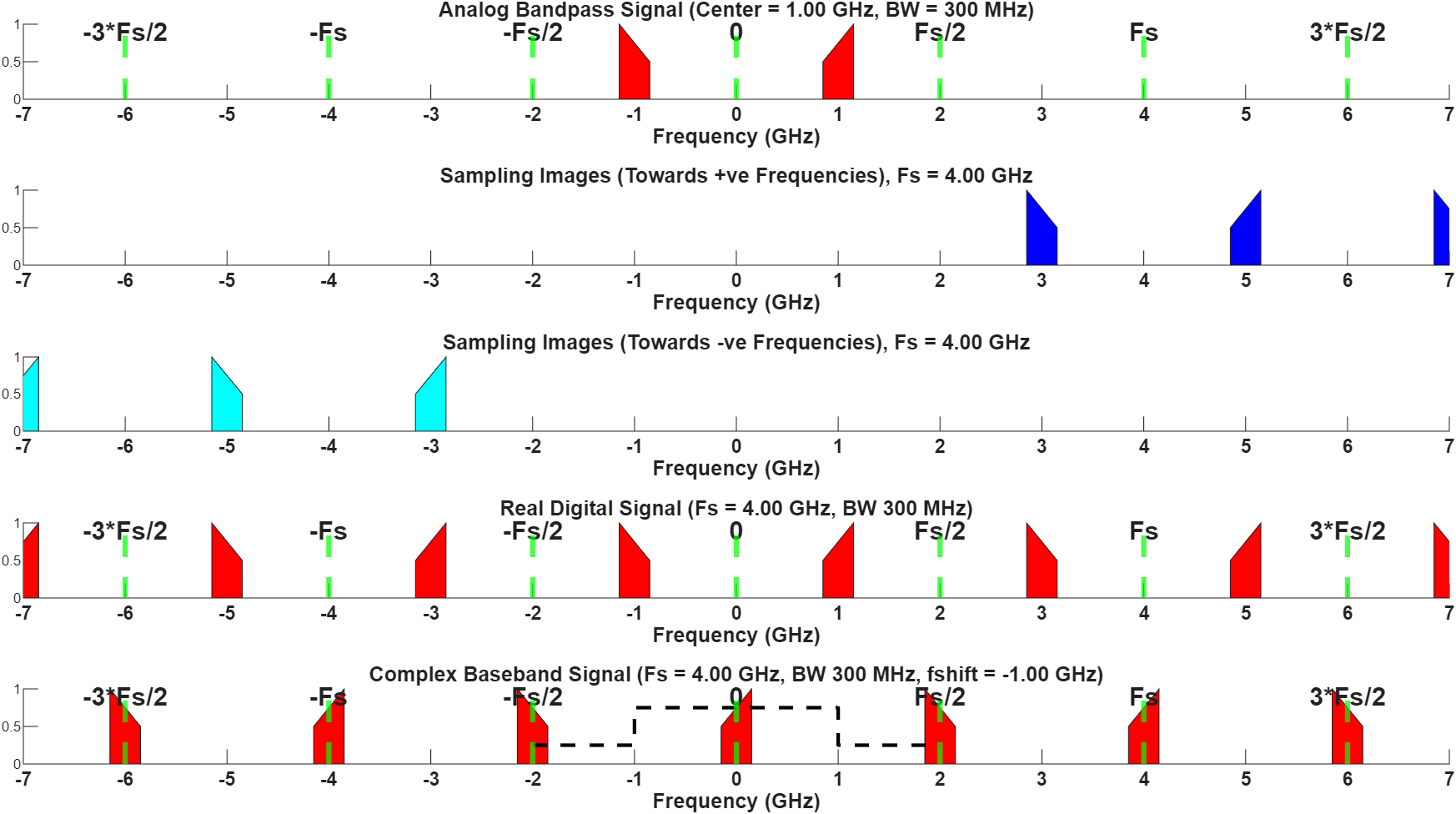

| Frequency Planner | Tune transceiver configuration and view frequency responses for RF devices (Since R2026a) |

Tools

| SoC Builder | Build, load, and execute SoC model on SoC, FPGA, and MCU boards |

| HDL IP Importer | Import HDL IP core into SoC model (Since R2023a) |

Functions

socModelAnalyzer | Estimate number of operations in Simulink model |

socFunctionAnalyzer | Estimate number of operations in MATLAB function |

socAlgorithmAnalyzerReport | Open algorithm analysis report |

socExportReferenceDesign | Export custom reference design for HDL Workflow Advisor |

socTaskSchedulability | Determine whether set of tasks can be scheduled for specified core assignments (Since R2022b) |

socCreateModel | Creates a skeleton SoC Blockset model for task set (Since R2022b) |

Objects

socModelBuilder | Build, load, and execute SoC model on SoC and FPGA boards (Since R2023a) |

Model Settings

Topics

Processor, Programmable Logic, and Memory

- SoC Blockset Model Structure

Top level structure of SoC model. - Use Template to Create SoC Model

Create SoC models using Simulink Project templates.

- Create an SoC Project Application

Step by step instructions and guidelines to create an SoC Blockset project and models for an SoC application.

- STEP 1: Project and Top-Level Model

- STEP 2: Software and Task Management on Processor

- STEP 3: User Logic on FPGA

- STEP 4: Memory and Register Channel Connections

- STEP 5: Simulation and Analysis

- SoC Generation Workflows

Choose between SoC Builder workflow or IP Core Generation workflow for deploying your design on an SoC device.

- Generate SoC Software Model

Generate Simulink software models using the IP core generation workflow. - Custom Hardware Board Configuration

Develop an SoC application model with a custom board configuration.

Application-Specific SoCs

- Use Template to Create SoC Model

Create SoC models using Simulink Project templates.

Architecture and Analysis

- Using the Algorithm Analyzer Report

Navigate details of the report generated by thesocModelAnalyzerorsocFunctionAnalyzerfunction.

Troubleshooting

Build Error When FPGA or Processor Model Not Detected

Unsupported mode in when generating SoC design using SoC Builder.

Build Error for Rapid Accelerator Mode

Unsupported simulation mode in SoC Blockset models and projects.