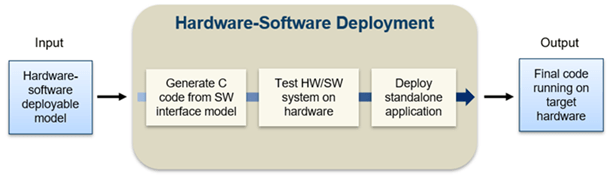

Hardware-Software Deployment

Generate C code (requires Embedded Coder®) from your software interface model and use external mode or processor-in-the-loop (PIL) mode to deploy and run your hardware-software model on target hardware. The input is a deployable model for your SoC device, which consists of:

A generated bitstream from your original model containing your HDL IP core.

A software interface model containing configured device drivers to allow communication between your processor and FPGA and C code generation for embedded processor.

The output is generated code for a hardware-software device running on your target hardware.

For more details on the workflow, see Targeting FPGA & SoC Hardware Overview.

Topics

- Choose a Method to Interact with IP Cores on Target Hardware

Choose a software interface method to interact with IP cores running on target hardware.

- Processor and FPGA Synchronization

In the HDL Workflow Advisor, you can choose a Processor/FPGA synchronization mode for your processor and FPGA when you generate a custom IP core to use in an embedded system integration project.