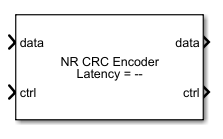

NR CRC Encoder

Generate CRC code bits and append them to input data

Libraries:

Wireless HDL Toolbox /

Error Detection and Correction

Description

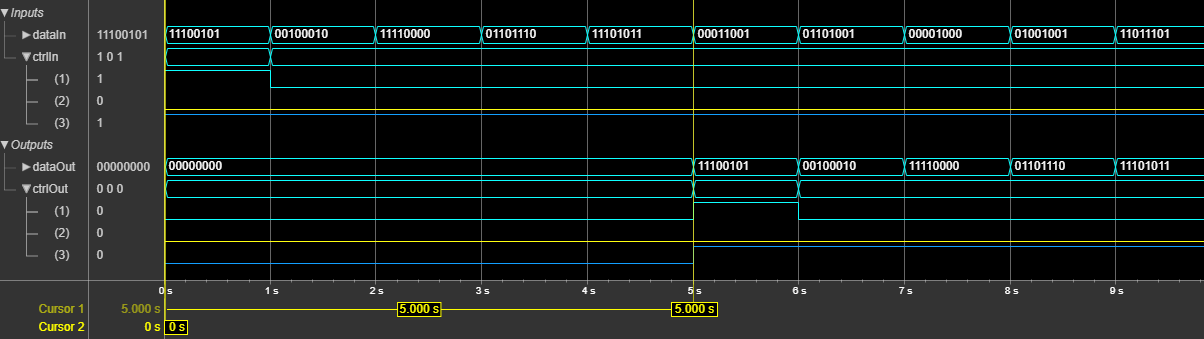

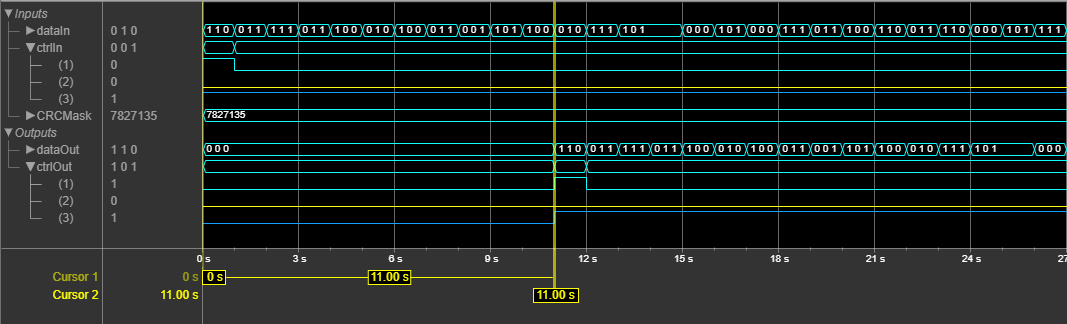

The NR CRC Encoder block calculates and generates a short, fixed-length binary sequence, known as the cyclic redundancy check (CRC) checksum, appends it to each frame of streaming data samples, and outputs CRC-encoded data. The block accepts and returns a data sample stream with accompanying control signals. The control signals indicate the validity of the samples and the boundaries of the frame.

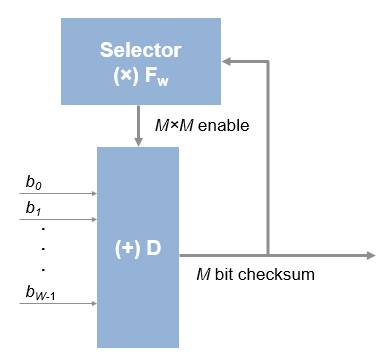

The block supports scalar and vector inputs and outputs data as either a scalar or vector based on the input data. To achieve higher throughput, the block accepts a binary vector or unsigned integer scalar input and implements a parallel architecture. The input data width must be less than or equal to the length of the CRC polynomial and the length of the CRC polynomial, must be divisible by the input data width. The block supports all CRC polynomials specified according to the 5G new radio (NR) standard 3GPP TS 38.212 [1]. When you select the CRC24C polynomial, the block supports dynamic CRC mask.

The block provides an interface and hardware-optimized architecture suitable for HDL code generation and hardware deployment.

Examples

Ports

Input

Output

Parameters

Algorithms

References

[1] 3GPP TS 38.212. “NR; Multiplexing and Channel Coding.” 3rd Generation Partnership Project; Technical Specification Group Radio Access Network.

[2] Campobello, G., G. Patane, and M. Russo. “Parallel CRC Realization.” IEEE Transactions on Computers 52, no. 10 (October 2003): 1312–19. https://doi.org/10.1109/TC.2003.1234528.

Extended Capabilities

Version History

Introduced in R2021a