Depuncturer

Reverse puncturing scheme to prepare for decoding

Libraries:

Wireless HDL Toolbox /

Error Detection and Correction

Description

The Depuncturer block replaces punctured symbols with neutral values as directed by an input puncture vector. The block returns erasure bits, which indicate the presence of neutral symbols in the output data stream. The block supports continuous and frame modes of operation. It provides an interface and architecture suitable for HDL code generation and hardware deployment.

Many wireless communication standards implement different code rates by puncturing patterns with a base code rate 1/2. The input to the block is a stream of one sample at a time. You can provide samples represented by hard-decision binary values or soft-decision log-likelihood ratios (LLR). The block returns output samples as 2-by-1 vectors.

The inserted neutral value depends on the data type of the input sample. For details, see the input data port.

Examples

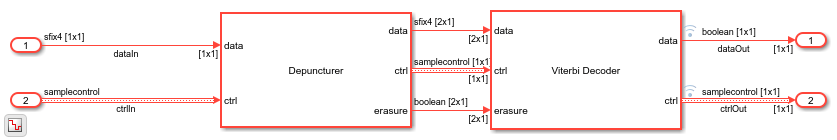

Depuncture and Decode Streaming Samples

Use Depuncturer and Viterbi Decoder blocks to decode samples encoded at WLAN code rates.

Ports

Input

Input sample, specified as a scalar. The block inserts a neutral value at punctured locations based on the data type of the input samples.

| Input Data Type | Inserted Neutral Value |

|---|---|

| 0 |

fixdt(0,WL,0) | 2(WL-1) |

uint8 | 128 |

uint16 | 32768 |

| 0 |

The block treats the input as hard-decision samples when the input

type is Boolean or fixdt(0,1,0).

For signed and unsigned numeric types, the block assumes soft-decision

samples. The block treats samples as signed integers for

single and double data types,

but these data types are not supported for HDL code generation.

The input sample must have a word length less than or equal to 16 bits, and a fraction length of 0 bits.

Data Types: int8 | int16 | uint8 | uint16 | Boolean | fixdt(0,1,0) | fixdt(S,WL,0) | single | double

Puncture vector, specified as a column vector of binary values. The

length of the puncture vector must be an even number in the range [4,

28]. The length must remain constant. The block removes initial zeros

from the provided vector, up to the first 1

(true). After the first 1

(true), the puncture vector cannot contain any

[1:0] subvector matching [0 0].

For example, IEEE 802.11 WLAN standard [1] supports

puncture rates 2/3, 3/4, and 5/6, with respective vector lengths of 4,

6, and 10. To support these multiple rates, set Puncture

vector source to Input port.

To support the largest vector size, the vector length must be 10 for all

rates. For 2/3 and 3/4 rates, pad the puncVector

input with zeros to create a 10-element vector. The puncture vector for

rate 3/4 is [1 1 0 1 1 0]'. For a vector length of

10, use [0 0 0 0 1 1 0 1 1 0]' as the input

puncVector.

When Operation mode is set to

Continuous, the block captures the value

of puncVector when both the

syncPunc and input valid

ports are 1 (true).

When Operation mode is set to

Frame, the block captures the value of

puncVector when both

ctrl.start and

ctrl.valid are

1 (true).

Dependencies

To enable this port, set Puncture vector

source to Input

port.

Data Types: Boolean

Puncture synchronization signal, specified as a

Boolean scalar value. This input is a control

signal that synchronizes the puncture vector input with the input

sample. When both syncPunc and

valid are 1

(true), the block aligns the puncture vector to

begin puncturing. The block captures the vector from either the

puncVector input port or the Puncture

vector parameter. The block ignores the

puncVector port when

syncPunc is 0

(false).

Dependencies

To enable this port, set Operation mode to

Continuous. When Operation

mode is Frame, the block

synchronizes the puncture vector using control signals in the input

ctrl bus.

Data Types: Boolean

Control signal that indicates when the sample from

data input port is valid. When

valid is 1 (true), the block

captures the values of the data input port. When

valid is 0 (false), the

block ignores the input samples.

Dependencies

To enable this port, set Operation mode to

Continuous.

Data Types: Boolean

Control signals accompanying the sample stream, specified as a

samplecontrol bus. The bus includes the

start, end, and

valid control signals, which indicate the

boundaries of the frame and the validity of the samples.

Dependencies

To enable this port, set Operation mode to

Frame.

Data Types: bus

Output

Output sample, returned as a 2-by-1 column vector. The data type is same as the data type of the input samples.

Data Types: int8 | int16 | uint8 | uint16 | Boolean | fixdt(0,1,0) | fixdt(S,WL,0) | single | double

Control signal that indicates when the sample from the

data output port is valid. The block sets the

valid port to 1

(true) when there is a valid sample on the output

data port.

Dependencies

To enable this port, set Operation mode to

Continuous.

Data Types: Boolean

Control signals accompanying the sample stream, returned as a

samplecontrol bus. The bus includes the

start, end, and

valid control signals, which indicate the

boundaries of the frame and the validity of the samples.

Dependencies

To enable this port, set Operation mode to

Frame.

Data Types: bus

Neutral symbol locations, returned as a 2-by-1 column vector

corresponding to the output samples. When erasure

is 1 (true), the corresponding

output data element is a depunctured neutral

value.

Data Types: Boolean

Parameters

End of frame behavior, specified as one of these modes:

Continuous– Allow changes to puncVector at any time. To force the block to capture the new puncture vector, set syncPunc to1(true). This waveform showsufix4input samples depunctured inContinuousmode.

Frame– You can only change puncVector at the start of a frame, indicated by ctrl.start. This waveform showsufix4input samples depunctured inFramemode.

Source of puncture vector, specified as either:

Input port– Specify the puncture vector using the puncVector port.Property– Specify the puncture vector using the Puncture vector parameter.

Puncture vector, specified as a column vector of binary values. The length of the puncture vector must be an even number in the range [4, 28]. The default value is the puncture vector for 3/4 code rate of IEEE 802.11 WLAN [1].

The puncture vector cannot contain any [1:0] subvector matching

[0 0].

Dependencies

To enable this port, set Puncture vector source

to Property.

Algorithms

The depuncturing algorithm shifts through each [1:0] subvector of the puncture vector. The subvector has three valid patterns: [0 1], [1 0], or [1 1]. Based on the subvector, neutral samples are inserted in place of punctured samples. The erasure output is the inverse of the puncture subvector. The block returns an error when it encounters the invalid subvector [0 0].

When you set Operation mode to

Continuous, the latency from valid input to valid

output in is seven cycles. When you set Operation mode to

Frame, the latency is six cycles.

These resource and performance data are the synthesis results from the generated

HDL targeted to an AMD®

Zynq®-7000 ZC706 board. The block is using ufix4 input

samples, in continuous mode with default settings. The design achieves a clock

frequency of 590 MHz.

| Resource | Number Used |

|---|---|

| LUT | 54 |

| FFS | 67 |

Xilinx® LogiCORE® DSP48 | 0 |

| Block RAM (16k) | 0 |

If you set Puncture vector source to

Property, the design uses fewer LUT and FFS

resources.

References

[1] IEEE Std 802.11ac™-2013 IEEE Standard for Information technology — Telecommunications and information exchange between systems — Local and metropolitan area networks — Specific requirements — Part 11: Wireless LAN Medium Access Control (MAC) and Physical Layer (PHY) Specifications — Amendment 4: Enhancements for Very High Throughput for Operation in Bands below 6 GHz.

Extended Capabilities

This block supports C/C++ code generation for Simulink® accelerator and rapid accelerator modes and for DPI component generation.

HDL Coder™ provides additional configuration options that affect HDL implementation and synthesized logic.

This block has one default HDL architecture.

| ConstrainedOutputPipeline | Number of registers to place at

the outputs by moving existing delays within your design. Distributed

pipelining does not redistribute these registers. The default is

|

| InputPipeline | Number of input pipeline stages

to insert in the generated code. Distributed pipelining and constrained

output pipelining can move these registers. The default is

|

| OutputPipeline | Number of output pipeline stages

to insert in the generated code. Distributed pipelining and constrained

output pipelining can move these registers. The default is

|

| SynthesisAttributes |

Specifies the synthesis attributes for the blocks and block output signals in the model. The generated HDL code contains these attributes. For more information, see SynthesisAttributes (HDL Coder). |

Version History

Introduced in R2018b

MATLAB Command

You clicked a link that corresponds to this MATLAB command:

Run the command by entering it in the MATLAB Command Window. Web browsers do not support MATLAB commands.

Select a Web Site

Choose a web site to get translated content where available and see local events and offers. Based on your location, we recommend that you select: .

You can also select a web site from the following list

How to Get Best Site Performance

Select the China site (in Chinese or English) for best site performance. Other MathWorks country sites are not optimized for visits from your location.

Americas

- América Latina (Español)

- Canada (English)

- United States (English)

Europe

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)