Using Command Line Functions to Support Changing Parameters

This example shows how to use Simulink® Design Verifier™ command-line functions to generate test data that incorporates different parameter values.

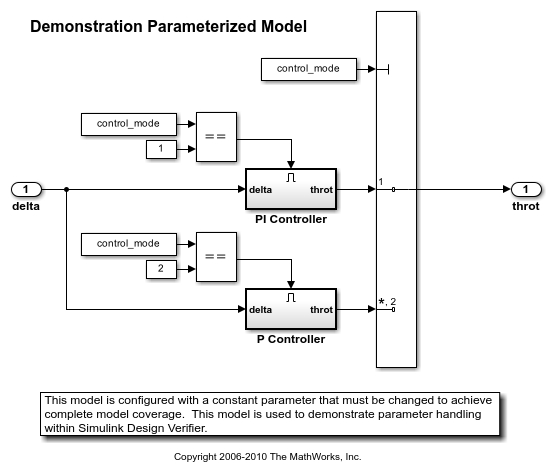

Controller Model with an Adjustable Parameter

The example model is a simple controller with a single parameter. The constant parameter 'control_mode' can be either 1 or 2. The parameter must take both values for the test cases to achieve complete coverage. The value determines the switch block output and which enabled subsystem will execute.

open_system('sldvdemo_param_controller');

Specifying Parameter Values for Analysis

Simulink Design Verifier does not identify parameter values. The tool uses the parameter values at the start of analysis for generating tests and proving properties. You can force the tool to incorporate changing parameter values by repeating analysis with different values.

The first iteration of design verifier will use control_mode=1.

control_mode = 1;

Simulink Design Verifier Options

Simulink Design Verifier functions use options objects created with the sldvoptions function to control all aspects of analysis and output.

In this example, we will run Simulink Design Verifier in test generation mode for a maximum of 300 seconds and produce a harness model. We will disable the report generation.

The default values of the remaining options are set correctly to generate tests. You can use the get command to display all the options and values.

opts = sldvoptions; opts.Mode = 'TestGeneration'; opts.MaxProcessTime = 300; opts.SaveHarnessModel = 'on'; opts.SaveReport = 'off'; opts.HarnessModelFileName = '$ModelName$_harness.slx';

Generating Tests and Collecting Coverage

The sldvgencov function generates test suites and model coverage together. All tests that can be generated with the current parameter values will be collected into the harness model and the resulting coverage returned in a coverage data object.

[status,coverageData,files] = sldvgencov('sldvdemo_param_controller',opts);

09-Apr-2026 09:54:05

Checking compatibility for test generation: model 'sldvdemo_param_controller'

Compiling model...done

Building model representation...done

09-Apr-2026 09:54:08

'sldvdemo_param_controller' is compatible for test generation with Simulink Design Verifier.

Generating tests...

..............

09-Apr-2026 09:54:14

Completed normally.

Generating output files:

Harness model:

/tmp/Bdoc26a_3222347_4094673/tpf29915fb/sldv-ex05697027/sldv_output/sldvdemo_param_controller/sldvdemo_param_controller_harness.slx

09-Apr-2026 09:54:19

Results generation completed.

Data file:

/tmp/Bdoc26a_3222347_4094673/tpf29915fb/sldv-ex05697027/sldv_output/sldvdemo_param_controller/sldvdemo_param_controller_sldvdata.mat

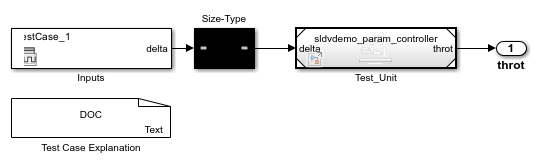

Integrating Parameter Initialization into a Test Harness

Generated test cases must be run with the same parameter values used during analysis. An initialization command configures the values during simulation of test cases. The sldvmergeharness function incorporates initialization commands into test harnesses.

initCmdStr = 'control_mode=1;'

[path,modelName] = fileparts(files.HarnessModel);

sldvmergeharness(modelName,modelName,initCmdStr);

initCmdStr =

'control_mode=1;'

Modifying Parameters and Repeating Test Generation

Modifying parameter values enables additional test generation. Passing a coverage data object as the third input to sldvgencov forces the function to ignore all model coverage test objectives that have been satisfied. We use the coverage data that was returned from the earlier call to sldvgencov to restrict test generation to unsatisfied test objectives.

control_mode=2;

[status,newCov,newFiles] = sldvgencov('sldvdemo_param_controller',opts,false,coverageData);

09-Apr-2026 09:54:23

Validating cached model representation from 09-Apr-2026 09:54:08...change detected

09-Apr-2026 09:54:23

Checking compatibility for test generation: model 'sldvdemo_param_controller'

Compiling model...done

Building model representation...done

09-Apr-2026 09:54:25

'sldvdemo_param_controller' is compatible for test generation with Simulink Design Verifier.

Generating tests...

..............

09-Apr-2026 09:54:30

Completed normally.

Generating output files:

Harness model:

/tmp/Bdoc26a_3222347_4094673/tpf29915fb/sldv-ex05697027/sldv_output/sldvdemo_param_controller/sldvdemo_param_controller_harness1.slx

09-Apr-2026 09:54:35

Results generation completed.

Data file:

/tmp/Bdoc26a_3222347_4094673/tpf29915fb/sldv-ex05697027/sldv_output/sldvdemo_param_controller/sldvdemo_param_controller_sldvdata1.mat

Merging Test Harnesses Into a Single Model

Another call to sldvharnessmerge merges the test data from the new harness and its initialization command into the existing harness model.

newInitCmd = 'control_mode=2;'

[path,newModelName] = fileparts(newFiles.HarnessModel);

sldvmergeharness(modelName,newModelName,newInitCmd);

newInitCmd =

'control_mode=2;'

Executing the Tests in the Harness Model

We close the second harness model that was created because the test cases have been merged into the first harness model. You can execute the suite of tests by clicking the 'Run all' button on the Signal Editor.

close_system(newModelName,0); sldvdemo_playall(modelName);

Clean Up

To complete the example, close the models and remove the generated files.

close_system(modelName,0);

close_system('sldvdemo_param_controller',0);

delete(files.HarnessModel);

delete(newFiles.HarnessModel);