Verify SerDes Toolbox CTLE in Architectural, Behavioral, and Circuit Domains

This example demonstrates a workflow to simulate a continuous-time linear equalizer (CTLE) in several design domains, while keeping the underlying models in synchronization through tool automation.

The model generated by SerDes Toolbox™ initially acts as a high-level specification of the desired analog circuit behavior. Using HDL Verifier™, the Simulink® CTLE model is exported into a SystemVerilog behavioral model that enables early digital control development for analog calibration before the analog circuit has been fully designed. Once designed, analog simulations can be used to characterize the circuit implementation of the CTLE. The simulation results are then fed-back into the Simulink architectural model, turning it into a circuit-representative Simulink model. The SystemVerilog behavioral model, which is frequently used for mixed-signal validation, can be regenerated via HDL Verifier; automatically turning the specification-based SystemVerilog model into a circuit-representative SystemVerilog model, thereby keeping the system, behavioral, and circuit models in synchronicity.

Introduction and Motivation

This example demonstrates a SystemVerilog behavioral export flow for a SerDes Toolbox CTLE. The CTLE is a common analog block for both analog-based and ADC-based SerDes. The CTLE is an analog high-pass filter that equalizes for channel loss. It also conditions the signal obtained from the channel for the subsequent equalizer stages or data samplers. The CTLE may be tunable depending on the SerDes standard targeted and its implementation. You can set the attenuation of the low-frequency signal components, relative to the high-frequency components, using digital control(s). Implementations that support further CTLE tuning capabilities are also possible, with increased circuit complexity.

This example generates a SystemVerilog model of a CTLE from a SerDes Toolbox generated model. It then demonstrates the equivalence in the open loop behavior of the CTLE model using Simulink and Verilog simulations. Finally, the example shows how you can use the SystemVerilog model to aid in digital circuit design and validation.

The supporting models, scripts, and HDL files are contained in a project.

openProject('serdes_ctle_proj');Create SerDes Simulink Model Using SerDes Toolbox

To create a design from SerDes Designer, export it to a Simulink model, and configure it for simulation follow these steps.

Create and Export SerDes Design to Simulink

Open the SerDes Designer app.

serdesDesigner

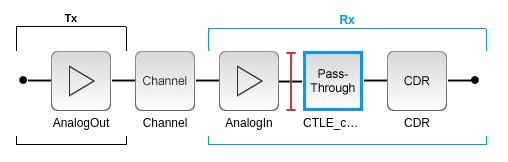

Add a Pass-Through and CDR block in the Rx path. To allow the use of an IBIS-AMI "In" parameter, do not instantiate a CTLE directly on this canvas. This enables hardware control of the Configuration Select parameter in SystemVerilog and IBIS simulations. You can setup the CTLE after exporting the model to Simulink.

Rename the Pass-Through block as "CTLE_core".

![]() Alternatively, you can load a provided SerDes Designer design from

Alternatively, you can load a provided SerDes Designer design from models/spec_CTLE_as_passthrough.mat.

Click the Export button to generate a Simulink model.

Configure CTLE and Parameterize Boost Setting in Simulink Model

Adjust this model to define the CTLE and allow targeting both IBIS-AMI and SystemVerilog workflows.

In the Rx subsystem, click the arrow in the lower left corner of the CTLE_core block to edit its contents.

Add a MATLAB System block and rename the System object to

serdes.CTLE.In the Main tab of the CTLE System object block parameter dialog box, set the Mode to

1, Specification toDC Gain and Peaking Gain, Peaking Frequency to20e9, DC Gain to0:-1:-20and Peaking Gain to0:20. Also select the ConfigSelectPort.In the Advanced tab, set the Symbol time (s) to the model workspace variable

SymbolTime, Sample interval (s) to the model workspace variableSampleInterval, Input Waveform Type toSample, CTLE adaptation optimization criteria control toSNR, and Filter Method toCascaded.Delete the PassThrough subsystem and replace it with the MATLAB System block.

Rename the MATLAB System block as

CTLE_core.In the top-level Rx subsystem, click the SerDes IBIS-AMI Manager annotation.

Select the AMI-Rx tab and the CTLE_core block. Click the Add Parameter button.

Create an input parameter named

ConfigSelect, also known as Boost, as shown below:

In the Rx/CTLE subsystem, attach the generated parameter block to the ConfigSelect input. Connect the ConfigSelect output to a terminator. The resulting Rx/CTLE subsystem should look like this:

Save the model as spec_CTLE_ibisami.slx.

![]() Alternatively, you can load the provided models/spec_CTLE_ibisami.slx instead.

Alternatively, you can load the provided models/spec_CTLE_ibisami.slx instead.

Configure Model and Generate SystemVerilog Component

Use the spec_CTLE_ibisami.slx model to generate IBIS-AMI models for use within the Serial Link Designer from Signal Integrity Toolbox™ app or a similar signal integrity simulator. You can also generate SystemVerilog behavioral models by changing some targeting parameters.

Configure Model to Target SystemVerilog

To set up the model for SystemVerilog generation follow these steps.

![]() Alternatively, you can skip these steps and use the provided model models/spec_CTLE_svdpi.slx.

Alternatively, you can skip these steps and use the provided model models/spec_CTLE_svdpi.slx.

Click "Save as..." and save as spec_CTLE_svdpi.slx.

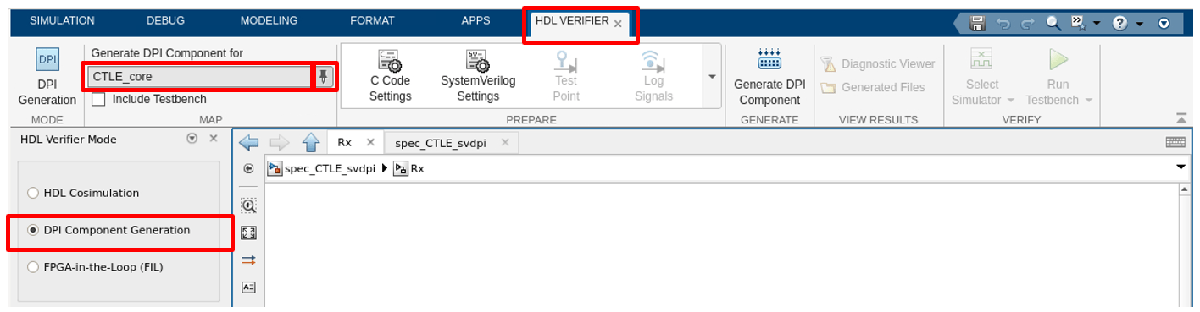

Open the HDL Verifier app from the Simulink Apps menu.

Select DPI Component Generation on the left pane.

Select the

Rx/CTLE_coresubsystem and pin it in the toolstrip.

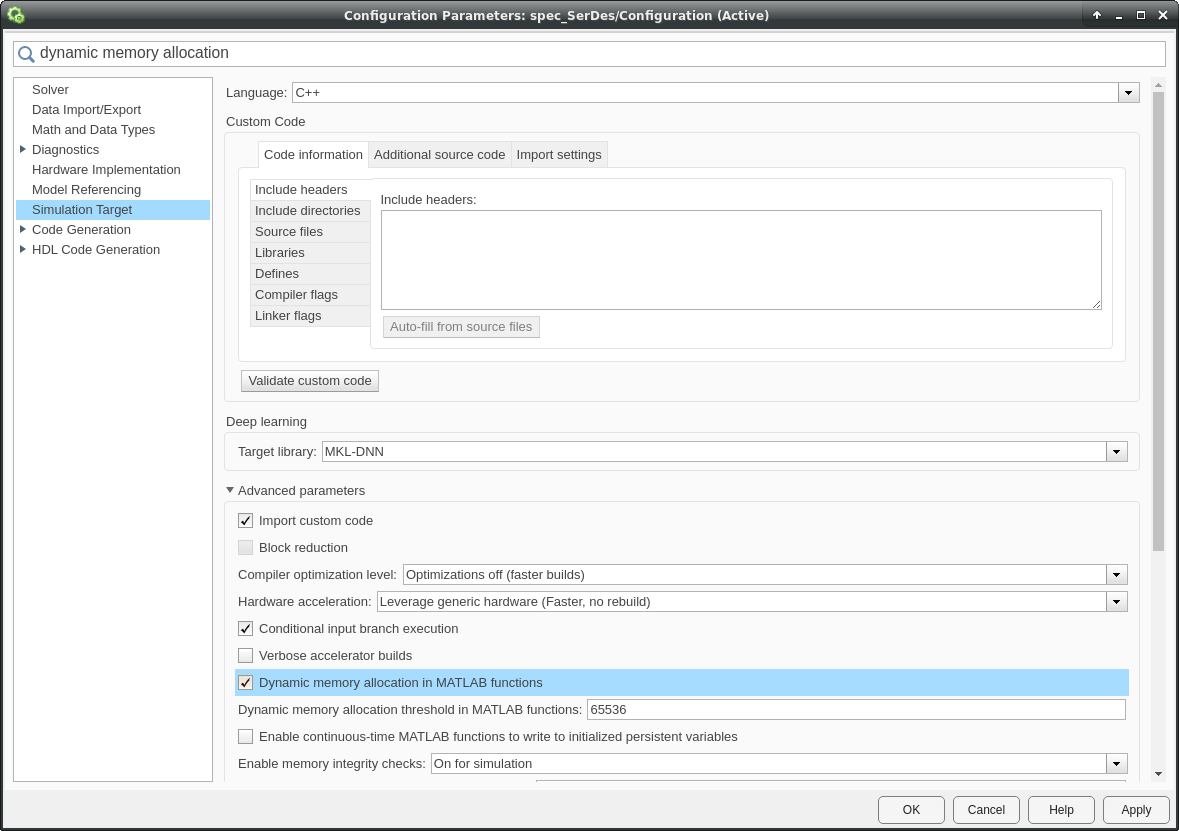

Click the C Code Settings button. For Toolchain, select

Automatically locate an installed toolchain.In the same configuration parameters window, type "dynamic memory allocation" in the search bar and enable Dynamic memory allocation in MATLAB functions.

SerDes Toolbox utilizes callback functions to seamlessly integrate into Simulink. However, these callbacks can interfere with DPI export flow via HDL Verifier. To disable the callbacks please run this command:

set_param('spec_CTLE_svdpi/Rx/CTLE_core', 'PreCopyFcn', '');

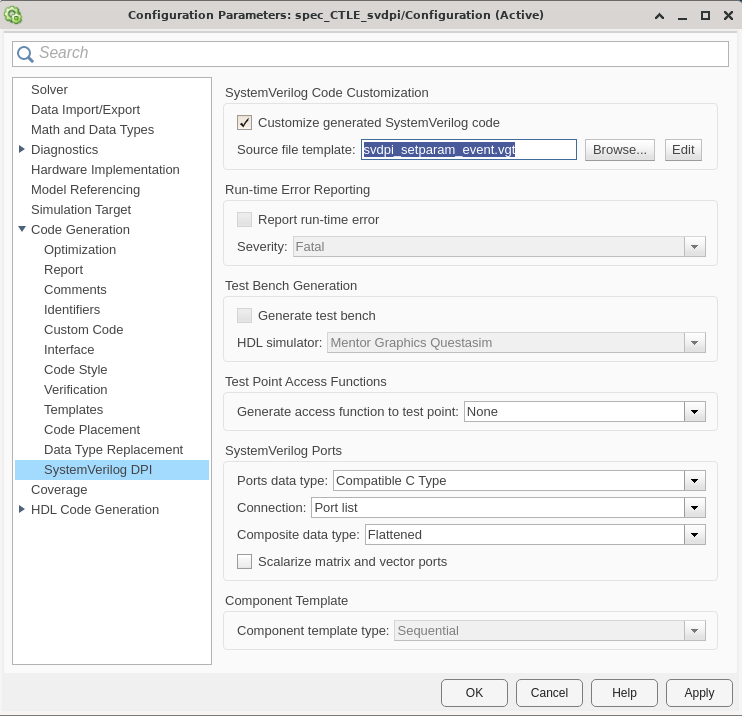

Since the component in HDL does not run off of a clock, the integration of the DPI model into the SystemVerilog-based system is best handled by using events to trigger the DPI calls. Select Customize generated SystemVerilog code and click on Browse. Navigate to your current working directory and then select scripts/svdpi_setparam_event.vgt.

Click OK to accept and dismiss the configuration parameter window.

Instrument Model for Comparing Simulink and SystemVerilog Simulation

Configure the model for comparing Simulink and SystemVerilog simulation results by naming the CTLE's input ctle_in and its output ctle_out. Select both signals, select the "..." and choose to log the signals.

Save the model as spec_CTLE_svdpi.slx.

![]() Alternatively, you can load the provided models/spec_CTLE_svdpi.slx instead.

Alternatively, you can load the provided models/spec_CTLE_svdpi.slx instead.

open_system('models/spec_CTLE_svdpi');SystemVerilog Generation

Turn off warnings about tunable parameters that will be optimized out since we are only concerned with tuning the ConfigSelect parameter.

warning('off','HDLLink:DPIG:AutoTunableVarMayBeOptimized');

The CTLE DPI model can then be built by clicking Generate DPI Component in the HDL Verifier tab.

Alternatively, you can generate the component via the command line:

slbuild('spec_CTLE_svdpi/Rx/CTLE_core');### Searching for referenced models in model 'CTLE_core'. ### Total of 1 models to build. ### Starting build procedure for model: CTLE_core ### Starting SystemVerilog DPI Component Generation ### Generating DPI H Wrapper CTLE_core_dpi.h ### Generating DPI-C Wrapper CTLE_core_dpi.c ### Generating SystemVerilog module CTLE_core_dpi.sv using template C:\ExampleManager\user.Bdoc.j2734697\shared_hdlv_serdes_mixed-ex34477068\serdes_ctle_proj\scripts\svdpi_setparam_event.vgt. ### Generating makefiles for: CTLE_core_dpi ### Invoking make to build the DPI Shared Library ### Successful completion of build procedure for model: CTLE_core Build Summary Top model targets: Model Build Reason Status Build Duration ===================================================================================== CTLE_core Global variable gpz changed. Code generated and compiled. 0h 1m 21.958s 1 of 1 models built (0 models already up to date) Build duration: 0h 1m 23.477s

The resulting DPI model will be available in the CTLE_core_build folder in the current working directory.

Correlate Simulink and SystemVerilog Models

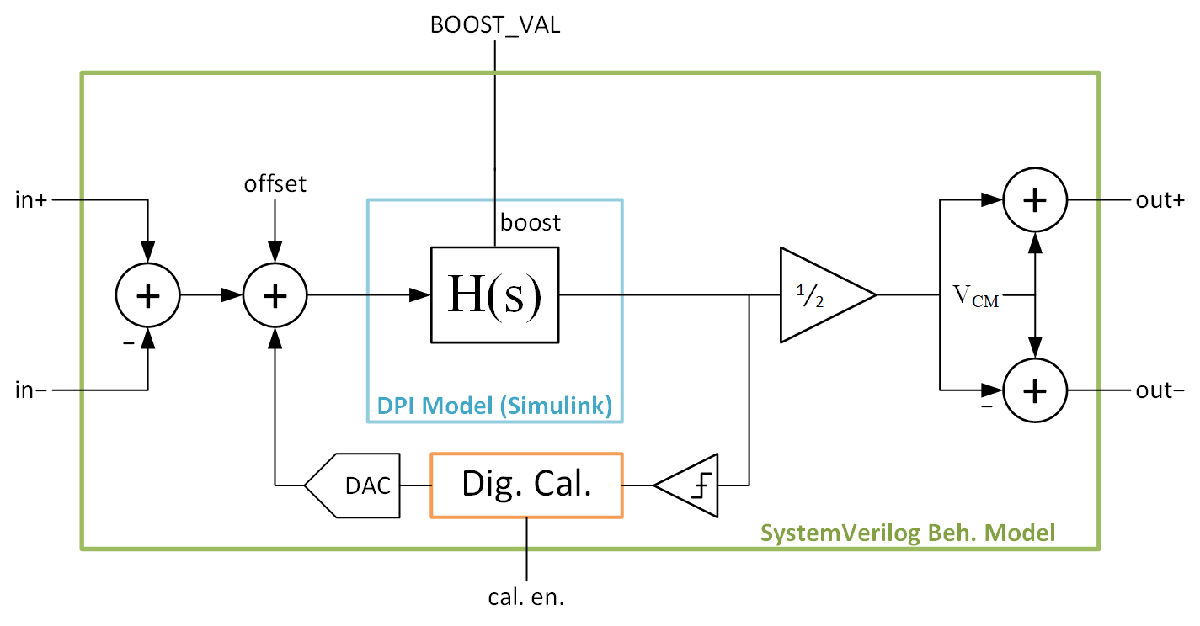

To run a suite of tests for different ConfigSelect/boost (BOOST_VAL) settings, 0, 10, and 19dB, use the provided ctle_run_cases script. This script first runs a Simulink simulation using a single BOOST_VAL setting. It then stores the input and output data into a BOOST_VAL indexed log file: simulink_out_b00.log for BOOST_VAL=0. Then, a Verilog simulation is run using the same BOOST_VAL setting. The Verilog simulation reads in the input waveform used for the Simulink simulation and applies it to the DPI CTLE model in the Verilog simulator. The provided CTLE testbench also creates a log file of the Verilog simulation: the files are named depending on the boost setting used: verilog_out_b00.log for BOOST_VAL=0. Note that the data is logged at the ctle.v module boundary, which is illustrated as the green box in the figure below; hence, the individual single-ended signals are stored. The contents of this file can be read back into the MATLAB® environment and plotted against the accompanying Simulink output using the ctle_plot_cases script. Note that you can also visualize a generated VCD file of the Verilog results outside of MATLAB, for example using GTKWaves.

The run script supports different HDL simulators. Edit the script to set up your path and environment for your simulator.

% This is a MathWorks-specific setup. You must assign PATH and % other settings specific to your environment for your chosen simulator. setup_questa();

Select the CTLE model to simulate.

% First, choose the model to simulate current_model = 'spec_CTLE_svdpi'; %#ok<*NASGU>

Then, choose an HDL Simulator.

% Uncomment one of the following supported HDL simulator choices: current_hdl_simulator = 'Questa'; % Windows or Linux % current_hdl_simulator = 'Xcelium'; % Linux only % current_hdl_simulator = 'VCS'; % Linux only % current_hdl_simulator = 'Vivado'; % Linux only % Run Simulink and HDL sim and plot results comparison ctle_run_cases

Reading pref.tcl

# 2022.2

# do {scripts\ctle_tb_tran_questa.do}

# 0

# Environment BOOST_VAL=0

# ** Warning: (vlib-34) Library already exists at "work".

# Errors: 0, Warnings: 1

# QuestaSim-64 vlog 2022.2 Compiler 2022.04 Apr 25 2022

# Start time: 15:55:02 on Sep 30,2024

# vlog -sv CTLE_core_build/CTLE_core_dpi.sv

# -- Compiling module CTLE_core_dpi

#

# Top level modules:

# CTLE_core_dpi

# End time: 15:55:03 on Sep 30,2024, Elapsed time: 0:00:01

# Errors: 0, Warnings: 0

# QuestaSim-64 vlog 2022.2 Compiler 2022.04 Apr 25 2022

# Start time: 15:55:04 on Sep 30,2024

# vlog -sv hdl_rtl/ctle_cm_cal.v hdl_rtl/ctle.v hdl_tb/ctle_tb_tran.v

# -- Compiling module ctle_cm_cal

# -- Compiling module ctle

# -- Compiling module ctle_tb_tran

#

# Top level modules:

# ctle_tb_tran

# End time: 15:55:05 on Sep 30,2024, Elapsed time: 0:00:01

# Errors: 0, Warnings: 0

# vsim -c -sv_lib CTLE_core_build/CTLE_core_win64 work.ctle_tb_tran "+BOOST_VAL=0"

# Start time: 15:55:06 on Sep 30,2024

# ** Note: (vsim-8009) Loading existing optimized design _opt2

# // Questa Sim-64

# // Version 2022.2 win64 Apr 25 2022

# //

# // Copyright 1991-2022 Mentor Graphics Corporation

# // All Rights Reserved.

# //

# // QuestaSim and its associated documentation contain trade

# // secrets and commercial or financial information that are the property of

# // Mentor Graphics Corporation and are privileged, confidential,

# // and exempt from disclosure under the Freedom of Information Act,

# // 5 U.S.C. Section 552. Furthermore, this information

# // is prohibited from disclosure under the Trade Secrets Act,

# // 18 U.S.C. Section 1905.

# //

# Loading sv_std.std

# Loading work.ctle_tb_tran(fast)

# Loading .\CTLE_core_build/CTLE_core_win64.dll

# CTLE_TB: Running with boost = 0

# ** Note: $finish : hdl_tb/ctle_tb_tran.v(61)

# Time: 357121116 fs Iteration: 0 Instance: /ctle_tb_tran

# End time: 15:55:15 on Sep 30,2024, Elapsed time: 0:00:09

# Errors: 0, Warnings: 0

Reading pref.tcl

# 2022.2

# do {scripts\ctle_tb_tran_questa.do}

# 10

# Environment BOOST_VAL=10

# ** Warning: (vlib-34) Library already exists at "work".

# Errors: 0, Warnings: 1

# QuestaSim-64 vlog 2022.2 Compiler 2022.04 Apr 25 2022

# Start time: 15:55:55 on Sep 30,2024

# vlog -sv CTLE_core_build/CTLE_core_dpi.sv

# -- Compiling module CTLE_core_dpi

#

# Top level modules:

# CTLE_core_dpi

# End time: 15:55:56 on Sep 30,2024, Elapsed time: 0:00:01

# Errors: 0, Warnings: 0

# QuestaSim-64 vlog 2022.2 Compiler 2022.04 Apr 25 2022

# Start time: 15:55:57 on Sep 30,2024

# vlog -sv hdl_rtl/ctle_cm_cal.v hdl_rtl/ctle.v hdl_tb/ctle_tb_tran.v

# -- Compiling module ctle_cm_cal

# -- Compiling module ctle

# -- Compiling module ctle_tb_tran

#

# Top level modules:

# ctle_tb_tran

# End time: 15:55:58 on Sep 30,2024, Elapsed time: 0:00:01

# Errors: 0, Warnings: 0

# vsim -c -sv_lib CTLE_core_build/CTLE_core_win64 work.ctle_tb_tran "+BOOST_VAL=10"

# Start time: 15:55:59 on Sep 30,2024

# ** Note: (vsim-8009) Loading existing optimized design _opt2

# // Questa Sim-64

# // Version 2022.2 win64 Apr 25 2022

# //

# // Copyright 1991-2022 Mentor Graphics Corporation

# // All Rights Reserved.

# //

# // QuestaSim and its associated documentation contain trade

# // secrets and commercial or financial information that are the property of

# // Mentor Graphics Corporation and are privileged, confidential,

# // and exempt from disclosure under the Freedom of Information Act,

# // 5 U.S.C. Section 552. Furthermore, this information

# // is prohibited from disclosure under the Trade Secrets Act,

# // 18 U.S.C. Section 1905.

# //

# Loading sv_std.std

# Loading work.ctle_tb_tran(fast)

# Loading .\CTLE_core_build/CTLE_core_win64.dll

# CTLE_TB: Running with boost = 10

# ** Note: $finish : hdl_tb/ctle_tb_tran.v(61)

# Time: 357121116 fs Iteration: 0 Instance: /ctle_tb_tran

# End time: 15:56:06 on Sep 30,2024, Elapsed time: 0:00:07

# Errors: 0, Warnings: 0

Reading pref.tcl

# 2022.2

# do {scripts\ctle_tb_tran_questa.do}

# 19

# Environment BOOST_VAL=19

# ** Warning: (vlib-34) Library already exists at "work".

# Errors: 0, Warnings: 1

# QuestaSim-64 vlog 2022.2 Compiler 2022.04 Apr 25 2022

# Start time: 15:56:45 on Sep 30,2024

# vlog -sv CTLE_core_build/CTLE_core_dpi.sv

# -- Compiling module CTLE_core_dpi

#

# Top level modules:

# CTLE_core_dpi

# End time: 15:56:46 on Sep 30,2024, Elapsed time: 0:00:01

# Errors: 0, Warnings: 0

# QuestaSim-64 vlog 2022.2 Compiler 2022.04 Apr 25 2022

# Start time: 15:56:47 on Sep 30,2024

# vlog -sv hdl_rtl/ctle_cm_cal.v hdl_rtl/ctle.v hdl_tb/ctle_tb_tran.v

# -- Compiling module ctle_cm_cal

# -- Compiling module ctle

# -- Compiling module ctle_tb_tran

#

# Top level modules:

# ctle_tb_tran

# End time: 15:56:48 on Sep 30,2024, Elapsed time: 0:00:01

# Errors: 0, Warnings: 0

# vsim -c -sv_lib CTLE_core_build/CTLE_core_win64 work.ctle_tb_tran "+BOOST_VAL=19"

# Start time: 15:56:49 on Sep 30,2024

# ** Note: (vsim-8009) Loading existing optimized design _opt2

# // Questa Sim-64

# // Version 2022.2 win64 Apr 25 2022

# //

# // Copyright 1991-2022 Mentor Graphics Corporation

# // All Rights Reserved.

# //

# // QuestaSim and its associated documentation contain trade

# // secrets and commercial or financial information that are the property of

# // Mentor Graphics Corporation and are privileged, confidential,

# // and exempt from disclosure under the Freedom of Information Act,

# // 5 U.S.C. Section 552. Furthermore, this information

# // is prohibited from disclosure under the Trade Secrets Act,

# // 18 U.S.C. Section 1905.

# //

# Loading sv_std.std

# Loading work.ctle_tb_tran(fast)

# Loading .\CTLE_core_build/CTLE_core_win64.dll

# CTLE_TB: Running with boost = 19

# ** Note: $finish : hdl_tb/ctle_tb_tran.v(61)

# Time: 357121116 fs Iteration: 0 Instance: /ctle_tb_tran

# End time: 15:56:56 on Sep 30,2024, Elapsed time: 0:00:07

# Errors: 0, Warnings: 0

![Figure Time Domain Analysis Results contains an axes object and another object of type uipanel. The axes object with title Time Domain Eye, xlabel [ps], ylabel [V] contains 6 objects of type image, line.](../../examples/shared_hdlv_serdes_mixed/win64/SerDesCTLESimInABCDomainsExample_16.png)

The results of the Simulink and Verilog runs can be plotted using the provided ctle_plot_cases.m script, which plots all cases simulated using subplots in a single figure.

% Plot the Simulink and Verilog Simulation results

ctle_plot_cases

Notice that the output of the Verilog model is sample-by-sample equal to the Simulink output.

Modify CTLE with Simulated CTLE Data

The CTLE model used so far is a parameterized CTLE, where in the DC and peaking gains are specified as parameters in the block mask.

To visualize the response of the CTLE, click the Visualize Response button:

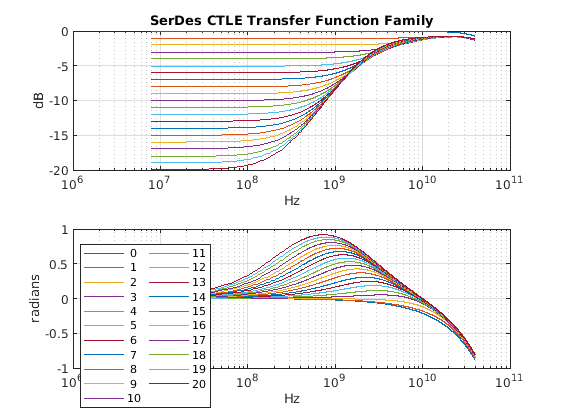

Once a circuit implementation of the CTLE is available, the simulated response of the CTLE can be used instead. In this example the measured CTLE responses for different control values were simulated. These responses were used to generate a gain-pole-zero (GPZ) rational fit. This data is stored as a GPZ matrix, in models/gpz.mat.

% Load the simulated response of the CTLE via GPZ load models/gpz

Open up the CTLE dialog, and change its Specification parameter from DC Gain and Peaking Gain to GPZ Matrix, and specify the Gain pole zero matrix as the previously loaded MATLAB environment variable gpz.

Visualizing the response of the filter, via the Visualize Response button, shows the CTLE frequency as shown below.

Notice that this frequency response has the same DC and boost gain values (0 - 20dB), but the circuit CTLE has a higher boost bandwidth than the specification based CTLE.

Save the updated Simulink model as circuit_CTLE_svdpi.slx to distinguish it from the spec_CTLE_svdpi.slx previously used.

Validate New CTLE behavior in Simulink and Verilog

We now revalidate the behavior in Simulink and SystemVerilog for the circuit-based gain CTLE. Continue from the previous step or open models/circuit_CTLE_svdpi.slx.

open_system('models/circuit_CTLE_svdpi.slx')First, regenerate the CTLE behavior for SystemVerilog by clicking the Generate DPI Component button in the toolstrip or by reinvoking the slbuild function.

slbuild('circuit_CTLE_svdpi/Rx/CTLE_core')### Searching for referenced models in model 'CTLE_core'. ### Total of 1 models to build. ### Starting build procedure for model: CTLE_core ### Starting SystemVerilog DPI Component Generation ### Generating DPI H Wrapper CTLE_core_dpi.h ### Generating DPI-C Wrapper CTLE_core_dpi.c ### Generating SystemVerilog module CTLE_core_dpi.sv using template C:\ExampleManager\user.Bdoc.j2734697\shared_hdlv_serdes_mixed-ex34477068\serdes_ctle_proj\scripts\svdpi_setparam_event.vgt. ### Generating makefiles for: CTLE_core_dpi ### Invoking make to build the DPI Shared Library ### Successful completion of build procedure for model: CTLE_core Build Summary Top model targets: Model Build Reason Status Build Duration ======================================================================================== CTLE_core Generated code was out of date. Code generated and compiled. 0h 1m 20.709s 1 of 1 models built (0 models already up to date) Build duration: 0h 1m 21.743s

To evaluate the circuit-representative CTLE, you can reuse the MATLAB scripts and Verilog testbenches (used to validate and correlate the Simulink and Verilog models' prior behavior) without modifications.

Change the CTLE model to simulate, rerun the test-cases, and plot the results.

% First, choose the model to simulate current_model = 'circuit_CTLE_svdpi'; % Run Simulink and HDL sim and plot results comparison ctle_run_cases

Reading pref.tcl

# 2022.2

# do {scripts\ctle_tb_tran_questa.do}

# 0

# Environment BOOST_VAL=0

# ** Warning: (vlib-34) Library already exists at "work".

# Errors: 0, Warnings: 1

# QuestaSim-64 vlog 2022.2 Compiler 2022.04 Apr 25 2022

# Start time: 15:59:43 on Sep 30,2024

# vlog -sv CTLE_core_build/CTLE_core_dpi.sv

# -- Compiling module CTLE_core_dpi

#

# Top level modules:

# CTLE_core_dpi

# End time: 15:59:45 on Sep 30,2024, Elapsed time: 0:00:02

# Errors: 0, Warnings: 0

# QuestaSim-64 vlog 2022.2 Compiler 2022.04 Apr 25 2022

# Start time: 15:59:45 on Sep 30,2024

# vlog -sv hdl_rtl/ctle_cm_cal.v hdl_rtl/ctle.v hdl_tb/ctle_tb_tran.v

# -- Compiling module ctle_cm_cal

# -- Compiling module ctle

# -- Compiling module ctle_tb_tran

#

# Top level modules:

# ctle_tb_tran

# End time: 15:59:46 on Sep 30,2024, Elapsed time: 0:00:01

# Errors: 0, Warnings: 0

# vsim -c -sv_lib CTLE_core_build/CTLE_core_win64 work.ctle_tb_tran "+BOOST_VAL=0"

# Start time: 15:59:48 on Sep 30,2024

# ** Note: (vsim-8009) Loading existing optimized design _opt2

# // Questa Sim-64

# // Version 2022.2 win64 Apr 25 2022

# //

# // Copyright 1991-2022 Mentor Graphics Corporation

# // All Rights Reserved.

# //

# // QuestaSim and its associated documentation contain trade

# // secrets and commercial or financial information that are the property of

# // Mentor Graphics Corporation and are privileged, confidential,

# // and exempt from disclosure under the Freedom of Information Act,

# // 5 U.S.C. Section 552. Furthermore, this information

# // is prohibited from disclosure under the Trade Secrets Act,

# // 18 U.S.C. Section 1905.

# //

# Loading sv_std.std

# Loading work.ctle_tb_tran(fast)

# Loading .\CTLE_core_build/CTLE_core_win64.dll

# CTLE_TB: Running with boost = 0

# ** Note: $finish : hdl_tb/ctle_tb_tran.v(61)

# Time: 357121116 fs Iteration: 0 Instance: /ctle_tb_tran

# End time: 15:59:55 on Sep 30,2024, Elapsed time: 0:00:07

# Errors: 0, Warnings: 0

Reading pref.tcl

# 2022.2

# do {scripts\ctle_tb_tran_questa.do}

# 10

# Environment BOOST_VAL=10

# ** Warning: (vlib-34) Library already exists at "work".

# Errors: 0, Warnings: 1

# QuestaSim-64 vlog 2022.2 Compiler 2022.04 Apr 25 2022

# Start time: 16:00:35 on Sep 30,2024

# vlog -sv CTLE_core_build/CTLE_core_dpi.sv

# -- Compiling module CTLE_core_dpi

#

# Top level modules:

# CTLE_core_dpi

# End time: 16:00:36 on Sep 30,2024, Elapsed time: 0:00:01

# Errors: 0, Warnings: 0

# QuestaSim-64 vlog 2022.2 Compiler 2022.04 Apr 25 2022

# Start time: 16:00:37 on Sep 30,2024

# vlog -sv hdl_rtl/ctle_cm_cal.v hdl_rtl/ctle.v hdl_tb/ctle_tb_tran.v

# -- Compiling module ctle_cm_cal

# -- Compiling module ctle

# -- Compiling module ctle_tb_tran

#

# Top level modules:

# ctle_tb_tran

# End time: 16:00:38 on Sep 30,2024, Elapsed time: 0:00:01

# Errors: 0, Warnings: 0

# vsim -c -sv_lib CTLE_core_build/CTLE_core_win64 work.ctle_tb_tran "+BOOST_VAL=10"

# Start time: 16:00:39 on Sep 30,2024

# ** Note: (vsim-8009) Loading existing optimized design _opt2

# // Questa Sim-64

# // Version 2022.2 win64 Apr 25 2022

# //

# // Copyright 1991-2022 Mentor Graphics Corporation

# // All Rights Reserved.

# //

# // QuestaSim and its associated documentation contain trade

# // secrets and commercial or financial information that are the property of

# // Mentor Graphics Corporation and are privileged, confidential,

# // and exempt from disclosure under the Freedom of Information Act,

# // 5 U.S.C. Section 552. Furthermore, this information

# // is prohibited from disclosure under the Trade Secrets Act,

# // 18 U.S.C. Section 1905.

# //

# Loading sv_std.std

# Loading work.ctle_tb_tran(fast)

# Loading .\CTLE_core_build/CTLE_core_win64.dll

# CTLE_TB: Running with boost = 10

# ** Note: $finish : hdl_tb/ctle_tb_tran.v(61)

# Time: 357121116 fs Iteration: 0 Instance: /ctle_tb_tran

# End time: 16:00:46 on Sep 30,2024, Elapsed time: 0:00:07

# Errors: 0, Warnings: 0

Reading pref.tcl

# 2022.2

# do {scripts\ctle_tb_tran_questa.do}

# 19

# Environment BOOST_VAL=19

# ** Warning: (vlib-34) Library already exists at "work".

# Errors: 0, Warnings: 1

# QuestaSim-64 vlog 2022.2 Compiler 2022.04 Apr 25 2022

# Start time: 16:01:27 on Sep 30,2024

# vlog -sv CTLE_core_build/CTLE_core_dpi.sv

# -- Compiling module CTLE_core_dpi

#

# Top level modules:

# CTLE_core_dpi

# End time: 16:01:27 on Sep 30,2024, Elapsed time: 0:00:00

# Errors: 0, Warnings: 0

# QuestaSim-64 vlog 2022.2 Compiler 2022.04 Apr 25 2022

# Start time: 16:01:28 on Sep 30,2024

# vlog -sv hdl_rtl/ctle_cm_cal.v hdl_rtl/ctle.v hdl_tb/ctle_tb_tran.v

# -- Compiling module ctle_cm_cal

# -- Compiling module ctle

# -- Compiling module ctle_tb_tran

#

# Top level modules:

# ctle_tb_tran

# End time: 16:01:29 on Sep 30,2024, Elapsed time: 0:00:01

# Errors: 0, Warnings: 0

# vsim -c -sv_lib CTLE_core_build/CTLE_core_win64 work.ctle_tb_tran "+BOOST_VAL=19"

# Start time: 16:01:30 on Sep 30,2024

# ** Note: (vsim-8009) Loading existing optimized design _opt2

# // Questa Sim-64

# // Version 2022.2 win64 Apr 25 2022

# //

# // Copyright 1991-2022 Mentor Graphics Corporation

# // All Rights Reserved.

# //

# // QuestaSim and its associated documentation contain trade

# // secrets and commercial or financial information that are the property of

# // Mentor Graphics Corporation and are privileged, confidential,

# // and exempt from disclosure under the Freedom of Information Act,

# // 5 U.S.C. Section 552. Furthermore, this information

# // is prohibited from disclosure under the Trade Secrets Act,

# // 18 U.S.C. Section 1905.

# //

# Loading sv_std.std

# Loading work.ctle_tb_tran(fast)

# Loading .\CTLE_core_build/CTLE_core_win64.dll

# CTLE_TB: Running with boost = 19

# ** Note: $finish : hdl_tb/ctle_tb_tran.v(61)

# Time: 357121116 fs Iteration: 0 Instance: /ctle_tb_tran

# End time: 16:01:37 on Sep 30,2024, Elapsed time: 0:00:07

# Errors: 0, Warnings: 0

![Figure Time Domain Analysis Results contains an axes object and another object of type uipanel. The axes object with title Time Domain Eye, xlabel [ps], ylabel [V] contains 6 objects of type image, line.](../../examples/shared_hdlv_serdes_mixed/win64/SerDesCTLESimInABCDomainsExample_21.png)

% Plot the CTLE correlation results

ctle_plot_cases

Once again, the outputs of the Verilog and Simulink models match, sample by sample. Note that the increased boost bandwidth is visible in the time-domain simulation outputs: for higher boost settings, the lower-frequency components of the signal are not as severely attenuated, resulting in higher overall signal swing.

Closed-Loop Mixed-Signal Validation

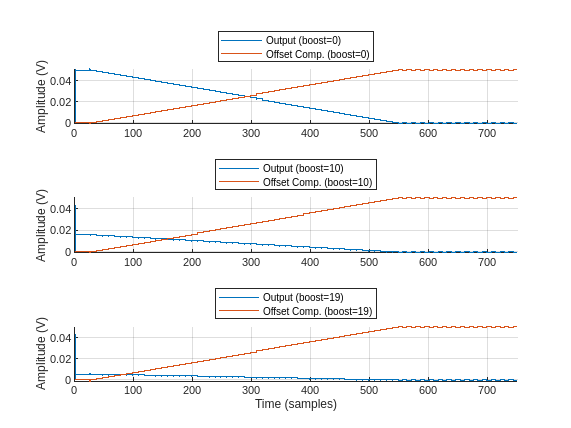

A powerful use-case for the DPI model is in the development and validation of mixed-signal subsystems. The CTLE is an analog circuit, and therefore after manufacturing it will have finite yet random input offset. If this offset is not canceled, it results in an offset in the output, which will be modulated by the CTLE's boost control. The CTLE's circuit offset is unlikely to be represented in the SerDes system model or in an IBIS model, as it is assumed that this offset is calibrated out during SerDes bring up. However, in order to test the SerDes calibration algorithm, the calibration algorithm must be represented by the behavioral model of the CTLE.

The CTLE Verilog model, that wraps the generated CTLE DPI, accounts for this random input offset, and also includes a simple implementation of an all-digital offset calibration engine.

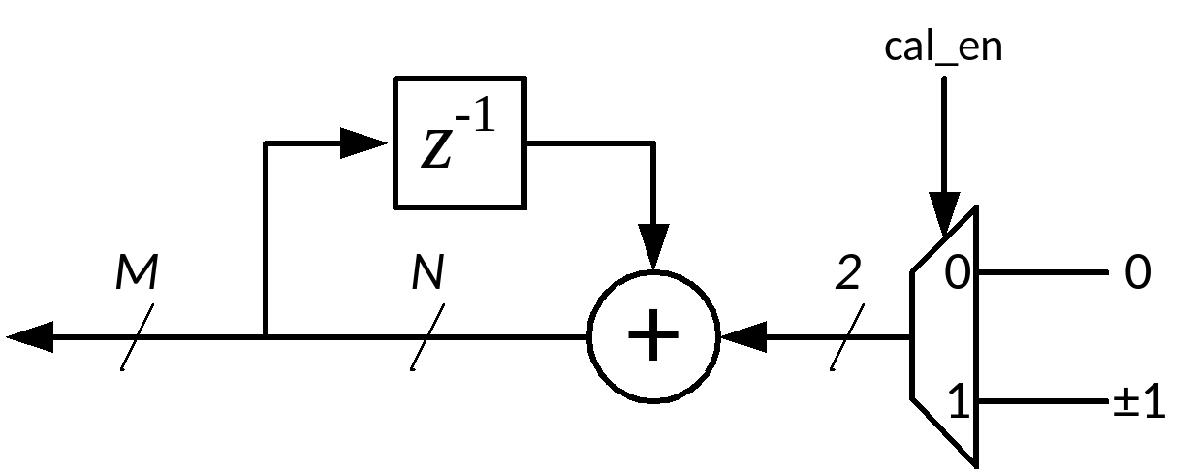

Review the contents of ctle.v. Note that it matches the block diagram.

The digital calibration engine implementation is based on a simple first order integrator. During calibration, the differential inputs of the CTLE are shorted to the common mode voltage, setting the differential input to 0V. The output of the CTLE is asynchronously sampled, and the input-offset DAC is driven in negative feedback to drive the effective input offset to zero.

Use the provided testbench (ctle_tb_offcomp.v) to validate the offset calibration engine using either the specification-based or circuit-based CTLE model.

% Run offset compensation test-cases

ctle_run_offset_calsReading pref.tcl

# 2022.2

# do {scripts\ctle_tb_offcomp_questa.do}

# 0

# Environment BOOST_VAL=0

# ** Warning: (vlib-34) Library already exists at "work".

# Errors: 0, Warnings: 1

# QuestaSim-64 vlog 2022.2 Compiler 2022.04 Apr 25 2022

# Start time: 16:01:55 on Sep 30,2024

# vlog -sv CTLE_core_build/CTLE_core_dpi.sv

# -- Compiling module CTLE_core_dpi

#

# Top level modules:

# CTLE_core_dpi

# End time: 16:01:56 on Sep 30,2024, Elapsed time: 0:00:01

# Errors: 0, Warnings: 0

# QuestaSim-64 vlog 2022.2 Compiler 2022.04 Apr 25 2022

# Start time: 16:01:57 on Sep 30,2024

# vlog -sv hdl_rtl/ctle_cm_cal.v hdl_rtl/ctle.v hdl_tb/ctle_tb_offcomp.v

# -- Compiling module ctle_cm_cal

# -- Compiling module ctle

# -- Compiling module ctle_tb_offcomp

#

# Top level modules:

# ctle_tb_offcomp

# End time: 16:01:58 on Sep 30,2024, Elapsed time: 0:00:01

# Errors: 0, Warnings: 0

# vsim -c -sv_lib CTLE_core_build/CTLE_core_win64 work.ctle_tb_offcomp "+BOOST_VAL=0"

# Start time: 16:01:59 on Sep 30,2024

# ** Note: (vsim-8009) Loading existing optimized design _opt

# // Questa Sim-64

# // Version 2022.2 win64 Apr 25 2022

# //

# // Copyright 1991-2022 Mentor Graphics Corporation

# // All Rights Reserved.

# //

# // QuestaSim and its associated documentation contain trade

# // secrets and commercial or financial information that are the property of

# // Mentor Graphics Corporation and are privileged, confidential,

# // and exempt from disclosure under the Freedom of Information Act,

# // 5 U.S.C. Section 552. Furthermore, this information

# // is prohibited from disclosure under the Trade Secrets Act,

# // 18 U.S.C. Section 1905.

# //

# Loading sv_std.std

# Loading work.ctle_tb_offcomp(fast)

# Loading .\CTLE_core_build/CTLE_core_win64.dll

# CTLE_TB_OFFCOMP: Running with boost = 0

# ** Note: $finish : hdl_tb/ctle_tb_offcomp.v(55)

# Time: 750 ns Iteration: 1 Instance: /ctle_tb_offcomp

# End time: 16:02:07 on Sep 30,2024, Elapsed time: 0:00:08

# Errors: 0, Warnings: 0

Reading pref.tcl

# 2022.2

# do {scripts\ctle_tb_offcomp_questa.do}

# 10

# Environment BOOST_VAL=10

# ** Warning: (vlib-34) Library already exists at "work".

# Errors: 0, Warnings: 1

# QuestaSim-64 vlog 2022.2 Compiler 2022.04 Apr 25 2022

# Start time: 16:02:21 on Sep 30,2024

# vlog -sv CTLE_core_build/CTLE_core_dpi.sv

# -- Compiling module CTLE_core_dpi

#

# Top level modules:

# CTLE_core_dpi

# End time: 16:02:22 on Sep 30,2024, Elapsed time: 0:00:01

# Errors: 0, Warnings: 0

# QuestaSim-64 vlog 2022.2 Compiler 2022.04 Apr 25 2022

# Start time: 16:02:23 on Sep 30,2024

# vlog -sv hdl_rtl/ctle_cm_cal.v hdl_rtl/ctle.v hdl_tb/ctle_tb_offcomp.v

# -- Compiling module ctle_cm_cal

# -- Compiling module ctle

# -- Compiling module ctle_tb_offcomp

#

# Top level modules:

# ctle_tb_offcomp

# End time: 16:02:24 on Sep 30,2024, Elapsed time: 0:00:01

# Errors: 0, Warnings: 0

# vsim -c -sv_lib CTLE_core_build/CTLE_core_win64 work.ctle_tb_offcomp "+BOOST_VAL=10"

# Start time: 16:02:25 on Sep 30,2024

# ** Note: (vsim-8009) Loading existing optimized design _opt

# // Questa Sim-64

# // Version 2022.2 win64 Apr 25 2022

# //

# // Copyright 1991-2022 Mentor Graphics Corporation

# // All Rights Reserved.

# //

# // QuestaSim and its associated documentation contain trade

# // secrets and commercial or financial information that are the property of

# // Mentor Graphics Corporation and are privileged, confidential,

# // and exempt from disclosure under the Freedom of Information Act,

# // 5 U.S.C. Section 552. Furthermore, this information

# // is prohibited from disclosure under the Trade Secrets Act,

# // 18 U.S.C. Section 1905.

# //

# Loading sv_std.std

# Loading work.ctle_tb_offcomp(fast)

# Loading .\CTLE_core_build/CTLE_core_win64.dll

# CTLE_TB_OFFCOMP: Running with boost = 10

# ** Note: $finish : hdl_tb/ctle_tb_offcomp.v(55)

# Time: 750 ns Iteration: 1 Instance: /ctle_tb_offcomp

# End time: 16:02:34 on Sep 30,2024, Elapsed time: 0:00:09

# Errors: 0, Warnings: 0

Reading pref.tcl

# 2022.2

# do {scripts\ctle_tb_offcomp_questa.do}

# 19

# Environment BOOST_VAL=19

# ** Warning: (vlib-34) Library already exists at "work".

# Errors: 0, Warnings: 1

# QuestaSim-64 vlog 2022.2 Compiler 2022.04 Apr 25 2022

# Start time: 16:02:48 on Sep 30,2024

# vlog -sv CTLE_core_build/CTLE_core_dpi.sv

# -- Compiling module CTLE_core_dpi

#

# Top level modules:

# CTLE_core_dpi

# End time: 16:02:49 on Sep 30,2024, Elapsed time: 0:00:01

# Errors: 0, Warnings: 0

# QuestaSim-64 vlog 2022.2 Compiler 2022.04 Apr 25 2022

# Start time: 16:02:50 on Sep 30,2024

# vlog -sv hdl_rtl/ctle_cm_cal.v hdl_rtl/ctle.v hdl_tb/ctle_tb_offcomp.v

# -- Compiling module ctle_cm_cal

# -- Compiling module ctle

# -- Compiling module ctle_tb_offcomp

#

# Top level modules:

# ctle_tb_offcomp

# End time: 16:02:50 on Sep 30,2024, Elapsed time: 0:00:00

# Errors: 0, Warnings: 0

# vsim -c -sv_lib CTLE_core_build/CTLE_core_win64 work.ctle_tb_offcomp "+BOOST_VAL=19"

# Start time: 16:02:52 on Sep 30,2024

# ** Note: (vsim-8009) Loading existing optimized design _opt

# // Questa Sim-64

# // Version 2022.2 win64 Apr 25 2022

# //

# // Copyright 1991-2022 Mentor Graphics Corporation

# // All Rights Reserved.

# //

# // QuestaSim and its associated documentation contain trade

# // secrets and commercial or financial information that are the property of

# // Mentor Graphics Corporation and are privileged, confidential,

# // and exempt from disclosure under the Freedom of Information Act,

# // 5 U.S.C. Section 552. Furthermore, this information

# // is prohibited from disclosure under the Trade Secrets Act,

# // 18 U.S.C. Section 1905.

# //

# Loading sv_std.std

# Loading work.ctle_tb_offcomp(fast)

# Loading .\CTLE_core_build/CTLE_core_win64.dll

# CTLE_TB_OFFCOMP: Running with boost = 19

# ** Note: $finish : hdl_tb/ctle_tb_offcomp.v(55)

# Time: 750 ns Iteration: 1 Instance: /ctle_tb_offcomp

# End time: 16:02:59 on Sep 30,2024, Elapsed time: 0:00:07

# Errors: 0, Warnings: 0

% Plot the results

ctle_plot_offset_cals

Note that you can develop and validate the algorithm and testbench for this offset calibration scheme ahead of time using the specification-based CTLE model. You can rerun the above test suite using that model by entering these commands in the MATLAB command line.

open models/spec_CTLE_svdpi.slx current_model = 'spec_CTLE_svdpi'; ctle_run_offset_cals

Reading pref.tcl

# 2022.2

# do {scripts\ctle_tb_offcomp_questa.do}

# 0

# Environment BOOST_VAL=0

# ** Warning: (vlib-34) Library already exists at "work".

# Errors: 0, Warnings: 1

# QuestaSim-64 vlog 2022.2 Compiler 2022.04 Apr 25 2022

# Start time: 16:03:17 on Sep 30,2024

# vlog -sv CTLE_core_build/CTLE_core_dpi.sv

# -- Compiling module CTLE_core_dpi

#

# Top level modules:

# CTLE_core_dpi

# End time: 16:03:18 on Sep 30,2024, Elapsed time: 0:00:01

# Errors: 0, Warnings: 0

# QuestaSim-64 vlog 2022.2 Compiler 2022.04 Apr 25 2022

# Start time: 16:03:19 on Sep 30,2024

# vlog -sv hdl_rtl/ctle_cm_cal.v hdl_rtl/ctle.v hdl_tb/ctle_tb_offcomp.v

# -- Compiling module ctle_cm_cal

# -- Compiling module ctle

# -- Compiling module ctle_tb_offcomp

#

# Top level modules:

# ctle_tb_offcomp

# End time: 16:03:20 on Sep 30,2024, Elapsed time: 0:00:01

# Errors: 0, Warnings: 0

# vsim -c -sv_lib CTLE_core_build/CTLE_core_win64 work.ctle_tb_offcomp "+BOOST_VAL=0"

# Start time: 16:03:21 on Sep 30,2024

# ** Note: (vsim-8009) Loading existing optimized design _opt

# // Questa Sim-64

# // Version 2022.2 win64 Apr 25 2022

# //

# // Copyright 1991-2022 Mentor Graphics Corporation

# // All Rights Reserved.

# //

# // QuestaSim and its associated documentation contain trade

# // secrets and commercial or financial information that are the property of

# // Mentor Graphics Corporation and are privileged, confidential,

# // and exempt from disclosure under the Freedom of Information Act,

# // 5 U.S.C. Section 552. Furthermore, this information

# // is prohibited from disclosure under the Trade Secrets Act,

# // 18 U.S.C. Section 1905.

# //

# Loading sv_std.std

# Loading work.ctle_tb_offcomp(fast)

# Loading .\CTLE_core_build/CTLE_core_win64.dll

# CTLE_TB_OFFCOMP: Running with boost = 0

# ** Note: $finish : hdl_tb/ctle_tb_offcomp.v(55)

# Time: 750 ns Iteration: 1 Instance: /ctle_tb_offcomp

# End time: 16:03:28 on Sep 30,2024, Elapsed time: 0:00:07

# Errors: 0, Warnings: 0

Reading pref.tcl

# 2022.2

# do {scripts\ctle_tb_offcomp_questa.do}

# 10

# Environment BOOST_VAL=10

# ** Warning: (vlib-34) Library already exists at "work".

# Errors: 0, Warnings: 1

# QuestaSim-64 vlog 2022.2 Compiler 2022.04 Apr 25 2022

# Start time: 16:03:42 on Sep 30,2024

# vlog -sv CTLE_core_build/CTLE_core_dpi.sv

# -- Compiling module CTLE_core_dpi

#

# Top level modules:

# CTLE_core_dpi

# End time: 16:03:43 on Sep 30,2024, Elapsed time: 0:00:01

# Errors: 0, Warnings: 0

# QuestaSim-64 vlog 2022.2 Compiler 2022.04 Apr 25 2022

# Start time: 16:03:44 on Sep 30,2024

# vlog -sv hdl_rtl/ctle_cm_cal.v hdl_rtl/ctle.v hdl_tb/ctle_tb_offcomp.v

# -- Compiling module ctle_cm_cal

# -- Compiling module ctle

# -- Compiling module ctle_tb_offcomp

#

# Top level modules:

# ctle_tb_offcomp

# End time: 16:03:45 on Sep 30,2024, Elapsed time: 0:00:01

# Errors: 0, Warnings: 0

# vsim -c -sv_lib CTLE_core_build/CTLE_core_win64 work.ctle_tb_offcomp "+BOOST_VAL=10"

# Start time: 16:03:46 on Sep 30,2024

# ** Note: (vsim-8009) Loading existing optimized design _opt

# // Questa Sim-64

# // Version 2022.2 win64 Apr 25 2022

# //

# // Copyright 1991-2022 Mentor Graphics Corporation

# // All Rights Reserved.

# //

# // QuestaSim and its associated documentation contain trade

# // secrets and commercial or financial information that are the property of

# // Mentor Graphics Corporation and are privileged, confidential,

# // and exempt from disclosure under the Freedom of Information Act,

# // 5 U.S.C. Section 552. Furthermore, this information

# // is prohibited from disclosure under the Trade Secrets Act,

# // 18 U.S.C. Section 1905.

# //

# Loading sv_std.std

# Loading work.ctle_tb_offcomp(fast)

# Loading .\CTLE_core_build/CTLE_core_win64.dll

# CTLE_TB_OFFCOMP: Running with boost = 10

# ** Note: $finish : hdl_tb/ctle_tb_offcomp.v(55)

# Time: 750 ns Iteration: 1 Instance: /ctle_tb_offcomp

# End time: 16:03:55 on Sep 30,2024, Elapsed time: 0:00:09

# Errors: 0, Warnings: 0

Reading pref.tcl

# 2022.2

# do {scripts\ctle_tb_offcomp_questa.do}

# 19

# Environment BOOST_VAL=19

# ** Warning: (vlib-34) Library already exists at "work".

# Errors: 0, Warnings: 1

# QuestaSim-64 vlog 2022.2 Compiler 2022.04 Apr 25 2022

# Start time: 16:04:09 on Sep 30,2024

# vlog -sv CTLE_core_build/CTLE_core_dpi.sv

# -- Compiling module CTLE_core_dpi

#

# Top level modules:

# CTLE_core_dpi

# End time: 16:04:10 on Sep 30,2024, Elapsed time: 0:00:01

# Errors: 0, Warnings: 0

# QuestaSim-64 vlog 2022.2 Compiler 2022.04 Apr 25 2022

# Start time: 16:04:11 on Sep 30,2024

# vlog -sv hdl_rtl/ctle_cm_cal.v hdl_rtl/ctle.v hdl_tb/ctle_tb_offcomp.v

# -- Compiling module ctle_cm_cal

# -- Compiling module ctle

# -- Compiling module ctle_tb_offcomp

#

# Top level modules:

# ctle_tb_offcomp

# End time: 16:04:12 on Sep 30,2024, Elapsed time: 0:00:01

# Errors: 0, Warnings: 0

# vsim -c -sv_lib CTLE_core_build/CTLE_core_win64 work.ctle_tb_offcomp "+BOOST_VAL=19"

# Start time: 16:04:13 on Sep 30,2024

# ** Note: (vsim-8009) Loading existing optimized design _opt

# // Questa Sim-64

# // Version 2022.2 win64 Apr 25 2022

# //

# // Copyright 1991-2022 Mentor Graphics Corporation

# // All Rights Reserved.

# //

# // QuestaSim and its associated documentation contain trade

# // secrets and commercial or financial information that are the property of

# // Mentor Graphics Corporation and are privileged, confidential,

# // and exempt from disclosure under the Freedom of Information Act,

# // 5 U.S.C. Section 552. Furthermore, this information

# // is prohibited from disclosure under the Trade Secrets Act,

# // 18 U.S.C. Section 1905.

# //

# Loading sv_std.std

# Loading work.ctle_tb_offcomp(fast)

# Loading .\CTLE_core_build/CTLE_core_win64.dll

# CTLE_TB_OFFCOMP: Running with boost = 19

# ** Note: $finish : hdl_tb/ctle_tb_offcomp.v(55)

# Time: 750 ns Iteration: 1 Instance: /ctle_tb_offcomp

# End time: 16:04:21 on Sep 30,2024, Elapsed time: 0:00:08

# Errors: 0, Warnings: 0

ctle_plot_offset_cals

Note that the plots are the same as in the previous run. This is because only the DC characteristics of the CTLE affect offset. The boost-frequency dependent or the boost-bandwidth dependent properties do not impact the offset-calibration algorithm.

Further Exploration

Try canceling out the DC offset by editing line 10 of hdl_tb/ctle_tb_offcomp.v to see what the correction limits of the digital algorithm are.

localparam offset = 0.05;

You can also change the frequency of the asynchronous sampler on line 9.

localparam async_freq = 400e6;

The frequency of the asynchronous sampler does not affect value it converges to, but rather the convergence time, that is the slope of the curves plotted earlier.

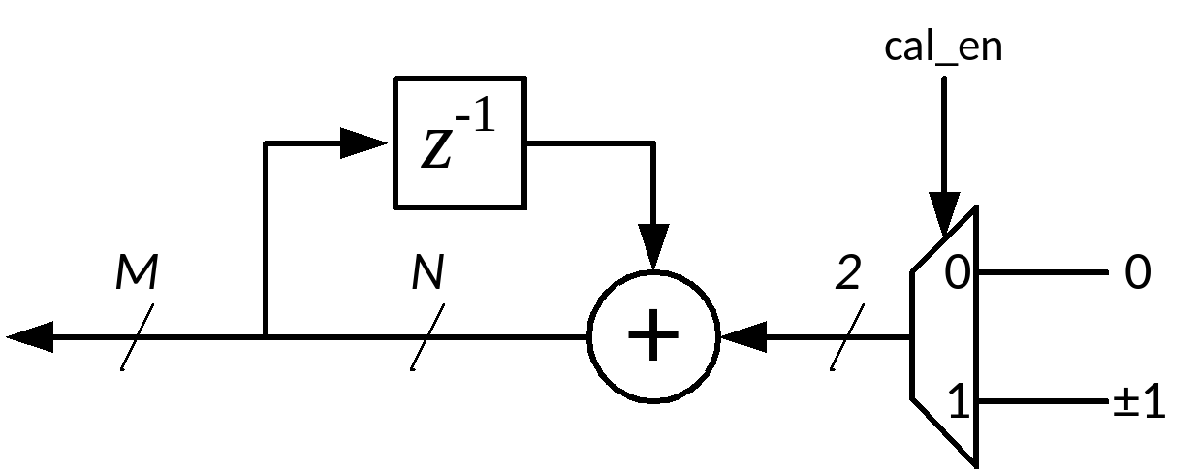

The digital algorithm is designed to be parametric as well, allowing you to control the width of the integrator (N, in the figure above) and how many of those bits drive the DAC (M). These values can be changed by editing lines 45 and 46 in hdl_rtl/ctle.v.

ctle_cm_cal #(

.out_width(7),

.int_width(9))

ctle_cm_cal (

where out_width is M and int_width is N

Resetting Models for IBIS-AMI and SystemVerilog Targeting

This example provides models for each step. In many workflows a single model is used during design iterations for the specification simulation, targeting the IBIS-AMI simulations and the SystemVerilog simulations. To reset any of the models used in this example to target either IBIS-AMI or SystemVerilog, invoke one of these functions.

reset_model_for_svdpi('model_name') reset_model_for_ibisami('model_name')

Conclusion

In this example you have created a design in the SerDes Designer app and exported it to Simulink. You then adjusted the model to use a CTLE with an IBIS-AMI parameter for ConfigSelect, that is also tunable in the SystemVerilog environment. You exported the CTLE using the SystemVerilog DPI generation target and confirmed the generated model's behavior against the original Simulink model. The CTLE was reconfigured using a GPZ matrix, regenerated for SystemVerilog, and verified to match the Simulink behavior. Finally, you confirmed that the SystemVerilog analog mixed-signal design properly handles offset calibration.

References

Validation Shift-Left: Enabling Early SerDes Mixed-Signal Validation, DesignCon 2022 conference paper, David Halupka, et al.

Find Zeros, Poles, and Gains for CTLE from Transfer Function

What Are Hammerstein-Wiener Models? (System Identification Toolbox)

Get Started with SystemVerilog DPI Component Generation (HDL Verifier)

Verify 5G Wireless Applications Using SystemVerilog DPI (HDL Verifier)