Supported EDA Tools and Hardware

Software

Microchip Libero SoC

Use this support package with these recommended versions:

Microchip Libero® SoC v2024.1

These features require a gold or platinum license from Microchip. For tool setup instructions, see Software Setup.

Software Setup

To use the Libero tool suite with HDL Verifier™ FPGA-in-the-loop (FIL), you must first add the FIL IP to Libero SoC Mega Vault.

Software Setup with an Internet Connection

To add the FIL IP to Libero SoC using an internet connection, follow these steps:

Launch Libero SoC.

From the Libero SoC menu, select View > Windows > Catalog to open the Catalog pane.

Click the Download them now! button to start downloading.

The IP catalog list now includes Solution-FIL-HSP-IP.

Close Libero SoC.

Launch MATLAB®.

Set

hdlsetuptoolpathto point to the Libero SoC installation. For example:hdlsetuptoolpath('ToolName','Microchip Libero SoC',... 'ToolPath','C:\Microsemi\Libero_SoC_v23.2\Designer\bin\libero.exe')

Software Setup Without Internet Connection

To add the FIL IP to Libero SoC with no internet connection, follow these steps:

On a machine with internet connection, navigate to the Libero SoC Downloads page.

Download the desired version of Mega Vault, and copy it to a portable storage device (such as a USB drive).

Connect the storage device to the target machine, copy the Mega Vault file to the local machine, then unzip this file.

Launch Libero SoC.

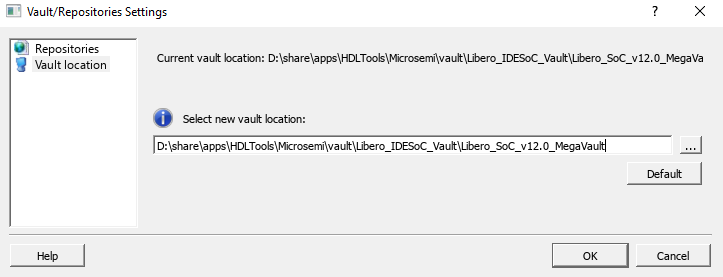

From the Libero SoC menu, select Project > Vault/Repositories Settings > Vault location. Set the path to the Mega Vault location.

Close Libero SoC.

Launch MATLAB.

Set

hdlsetuptoolpathto point to the Libero SoC installation. For example:hdlsetuptoolpath('ToolName','Microchip Libero SoC',... 'ToolPath','C:\Microsemi\Libero_SoC_v23.2\Designer\bin\libero.exe')

Required IP Cores for FPGA-in-the-Loop

Installing Microchip Mega-Vault, enables access to the required IP cores for FIL simulation. You can choose to download only the required IP cores.

Microchip SmartFusion® 2 requires

Microsemi:SolutionCore:idu_topMicrochip Polarfire® requires:

Actel:SgCore:PF_CCCMicrosemi:SolutionCore:iog_cdr_test_wrapper

RTG4® requires:

Actel:SgCore:RTG4FCCCMicrosemi:SolutionCore:CM1_TOP

Board Connections

Ethernet Connection

You can run FPGA-in-the-loop over an Ethernet connection.

| Required Hardware | Supported Interfaces | Required Software |

|---|---|---|

|

| There are no software requirements for an Ethernet connection, but ensure that the firewall on the host computer does not prevent UDP communication. |