HDL Code Generation

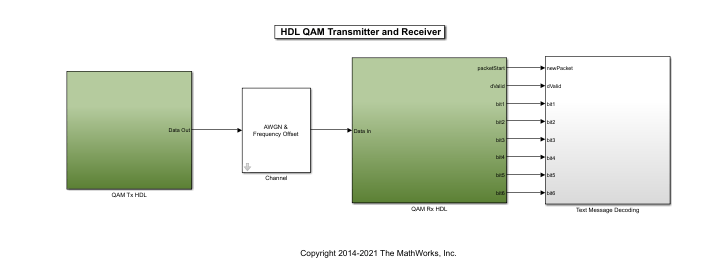

Use HDL Coder™ features to implement communications system designs on FPGAs or ASICs. You can generate synthesizable and portable VHDL® and Verilog® code, and generate VHDL and Verilog test benches for quickly simulating, testing, and verifying the generated code. You can generate code from Simulink or MATLAB designs. This support includes error correction and detection, modulation, filters, mathematical and signal operations, and other algorithms optimized for resource use and performance, such as the NCO (DSP HDL Toolbox) block. For a basic example of how to generate HDL code, see Programmable FIR Filter for FPGA.

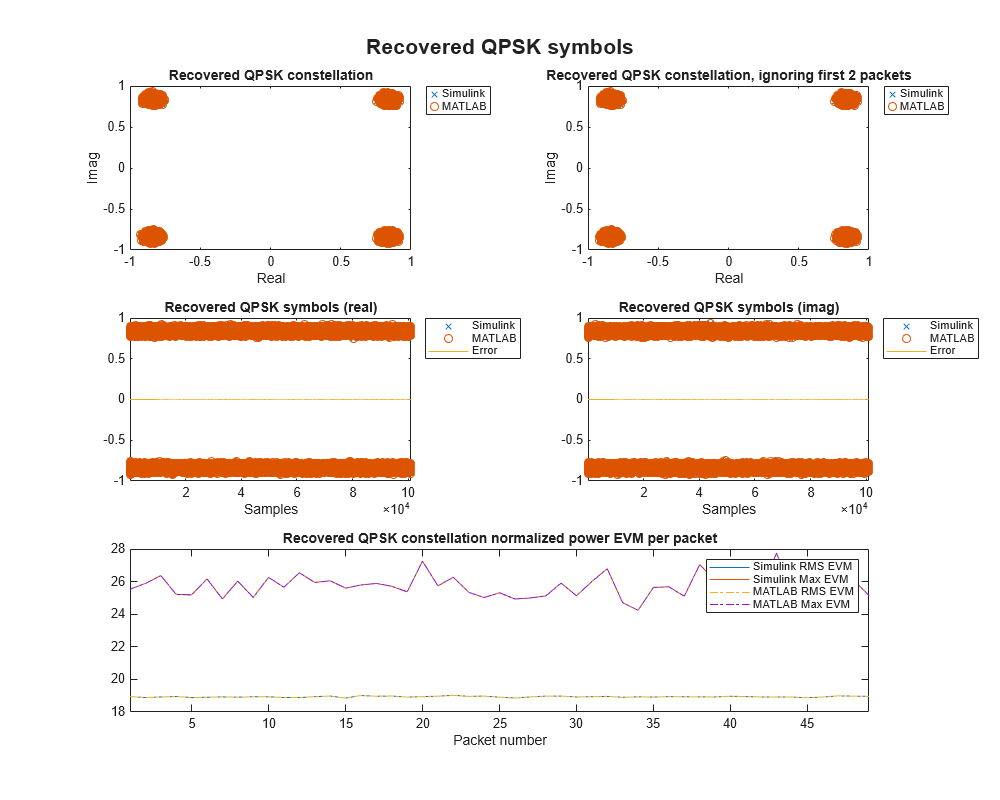

To visualize and debug your designs in Simulink or MATLAB, use the Logic Analyzer waveform viewer.

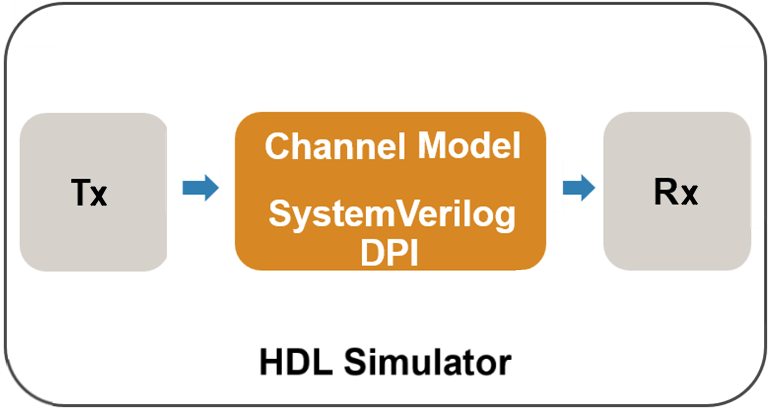

HDL Verifier™ features enable you to reuse communications system models in your HDL design environment. You can verify generated or hand-written HDL designs against behavioral reference models in Simulink or MATLAB, debug designs in simulators or hardware, and generate testbenches and verification IP.

Topics

- Find Blocks That Support HDL Code Generation

Filter for blocks that support HDL code generation in the Simulink library browser and in documentation.

- Wireless Communications Design for ASICs, FPGAs, and SoCs

Design wireless communication algorithms for hardware by using Wireless HDL Toolbox™ blocks.

Simulink Visualization Tool

| Logic Analyzer | Visualize, measure, and analyze transitions and states over time |