FFT 1536

Computes fast-fourier-transform (FFT) for LTE standard transmission bandwidth of 15 MHz

Libraries:

Wireless HDL Toolbox /

Modulation

Description

The FFT 1536 block is designed to support LTE standard transmission

bandwidth of 15 MHz. This block is used in LTE OFDM Demodulator block

operation. The block accepts input data, along with a valid control signal and outputs

streaming data with a samplecontrol bus.

The block provides an architecture suitable for HDL code generation and hardware deployment.

Examples

Application of FFT 1536 block in LTE OFDM Demodulation

Use FFT 1536 block in LTE OFDM demodulation.

Ports

Input

Input data, specified as a scalar of real or complex values.

double and

single data types are supported for simulation, but not for HDL

code generation.

The more the fractional bits you provide in the input word length, the better the accuracy you receive in the output.

Data Types: double | single | int8 | int16 | int32 | fixed point

Complex Number Support: Yes

Indicates if the input data is valid. When the input valid is

1 (true), the block captures the value on the input

data port. When the input valid is

0 (false), the block ignores the input data

samples.

Data Types: Boolean

When this value is 1 (true), the block stops the current

calculation and clears all internal states.

Dependencies

To enable this port, select the Enable reset input port parameter.

Data Types: Boolean

Output

Frequency channel output data, returned as a scalar of real or complex values.

When the input is of fixed point data type, the output data

type is the same as the input data type. When the input is of integer type, the output

data type is of fixed point type.

Data Types: double | single | int8 | int16 | int32 | fixed point

Complex Number Support: Yes

Control signals accompanying the sample stream, returned as a samplecontrol

bus. The bus includes the start, end, and

valid control signals, which indicate the boundaries of the frame

and the validity of the samples.

start— Indicates the start of the output frameend— Indicates the end of the output framevalid— Indicates that the data on the output data port is valid

For more details, see Sample Control Bus.

Data Types: bus

Parameters

Main

Specifies the complex multiplier type for HDL implementation. Each multiplication

is implemented either with Use 3 multipliers and 5 adders

or with Use 4 multipliers and 2 adders. The implementation

speed depends on the synthesis tool and the target device that you use.

Specifies the type of rounding method for internal fixed-point calculations. For

more information about rounding methods, see Rounding Modes. When the input is any integer or fixed-point data type,

this block uses fixed-point arithmetic for internal calculations. This parameter does

not apply when the input data is single or

double.

When you select this parameter, the block divides the output by 1536. This option

is useful when you want the output of the block to stay in the same amplitude range as

its input. You require this option when the input is of fixed point

type.

When you select this parameter, the output word length increases by 2 bits and when you clear this parameter the output word length increases by 11 bits.

Control Ports

Select this parameter to enable the reset port.

Algorithms

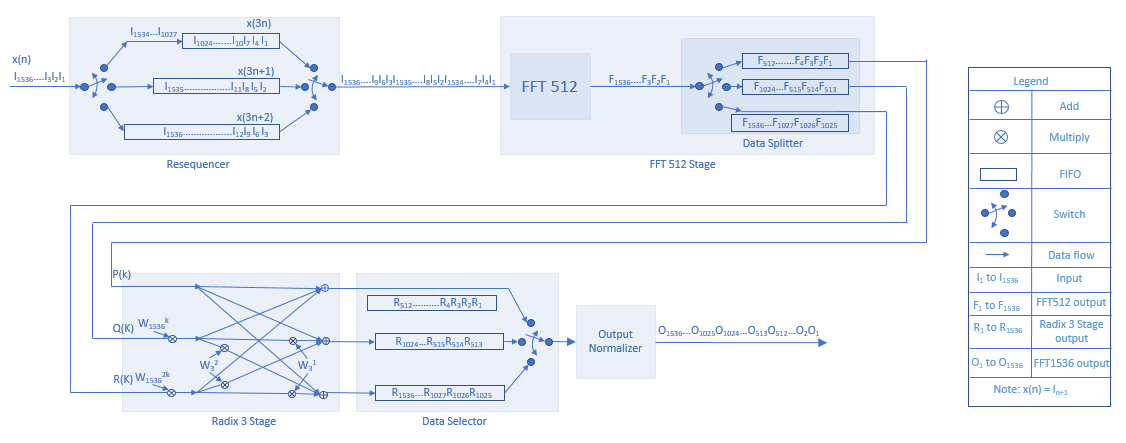

To design an FFT 1536 block, radix-3 decimation-in-time (DIT) algorithm is implemented. The input sequence x(n) for all n = {0,1,2....1535} is divided into three DIT sequences, x(3n), x(3n+1), x(3n+2) for all n = {0,1,2....511}.

This equation defines FFT 1536 computation of a given sequence x(n).

The equation can be implemented by dividing it into three parts, where P(k), Q(k), R(k) are the N/3 (FFT 512) point FFT of x(3n), x(3n+1), and x(3n+2), respectively. Here, N = 1536, and k = 0,1,2,.....,511.

This diagram shows the internal architecture of the block and how the input sequence streams through the components of the block.

The input sequence x(n) is demultiplexed into three DIT sequences, x(3n), x(3n+1), x(3n+2), each of length 512. Three first-input first-output (FIFO) memories store these sequences. These DIT sequences are serialized and streamed through the FFT 512 block.

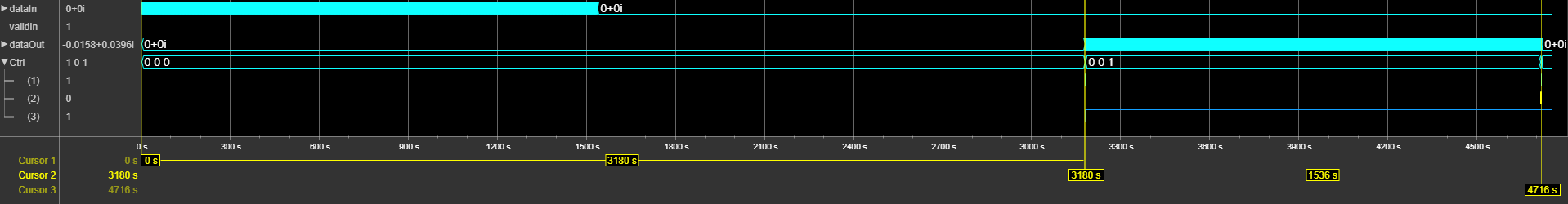

This image shows the output waveform of the block when operated with default

configuration parameters. The block provides output data after a latency of 3180 clock

cycles. The length of the output data between start

(Ctrl.(1)) and end (Ctrl.(2))

output control signals is 1536 clock cycles.

The performance of the synthesized HDL code varies with your target and synthesis

options. This table shows the resource and performance data synthesis results of the block

with default configuration parameters, along with normalization feature enabled, and with an

input data in fixdt(1,17,15) format. The generated HDL is targeted to

an AMD®

Zynq® XC7Z045-FFG900-2 FPGA board. The design achieves a clock frequency of 355

MHz.

| Resource | Number Used |

|---|---|

| LUTs | 7330 |

| Registers | 9325 |

| Block RAMs | 18 |

| DSPs | 36 |

Extended Capabilities

This block supports C/C++ code generation for Simulink® accelerator and rapid accelerator modes and for DPI component generation.

HDL Coder™ provides additional configuration options that affect HDL implementation and synthesized logic.

This block has one default HDL architecture.

| ConstrainedOutputPipeline | Number of registers to place at

the outputs by moving existing delays within your design. Distributed

pipelining does not redistribute these registers. The default is

|

| InputPipeline | Number of input pipeline stages

to insert in the generated code. Distributed pipelining and constrained

output pipelining can move these registers. The default is

|

| OutputPipeline | Number of output pipeline stages

to insert in the generated code. Distributed pipelining and constrained

output pipelining can move these registers. The default is

|

| SynthesisAttributes |

Specifies the synthesis attributes for the blocks and block output signals in the model. The generated HDL code contains these attributes. For more information, see SynthesisAttributes (HDL Coder). |

You cannot generate HDL for this block inside a Resettable Synchronous Subsystem (HDL Coder).

Version History

Introduced in R2019b

MATLAB Command

You clicked a link that corresponds to this MATLAB command:

Run the command by entering it in the MATLAB Command Window. Web browsers do not support MATLAB commands.

Select a Web Site

Choose a web site to get translated content where available and see local events and offers. Based on your location, we recommend that you select: .

You can also select a web site from the following list

How to Get Best Site Performance

Select the China site (in Chinese or English) for best site performance. Other MathWorks country sites are not optimized for visits from your location.

Americas

- América Latina (Español)

- Canada (English)

- United States (English)

Europe

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)