Transmit and Receive Tone Using AMD RFSoC Device - Part 2 Deployment

This example shows how to implement and verify a design on AMD® RFSoC device using SoC Blockset™. You deploy a system on AMD RFSoC evaluation kits that generates a sinusoidal tone from an FPGA, transmits it across multiple RF channels, and receives it back into the device to complete the loopback. For modeling and simulation of the system, see the Transmit and Receive Tone Using AMD RFSoC Device - Part 1 System Design example.

Supported Hardware Platforms:

AMD Zynq UltraScale®+ RFSoC ZCU111 evaluation kit + XM500 balun card

AMD Zynq UltraScale+ RFSoC ZCU216 evaluation kit + XM655 balun card

AMD Zynq UltraScale+ RFSoC ZCU208 evaluation kit + XM655 balun card

AMD Zynq UltraScale+ RFSoC DFE ZCU670 evaluation kit + XM755 balun card

Implement and Run on Hardware

Hardware Setup for ZCU111 Kit

Connect the SMA connectors on the XM500 balun card to complete the loopback between the DACs and ADCs, according to the connections provided in the following table. Use DC blocks for differential channels loopback.

To implement the soc_rfsoc_datacapture model on a supported SoC board, use the SoC Builder tool. Ensure that the Hardware Board option is set to Xilinx Zynq UltraScale+ RFSoC ZCU111 Evaluation Kit on the System on Chip tab of the Simulink toolstrip.

To open SoC Builder, click Configure, Build, & Deploy. After the SoC Builder tool opens, follow these steps:

On the Setup screen, select Build model. Click Next.

On the Select Build Action screen, select Build and load for external mode. Click Next.

On the Select Project Folder screen, specify the project folder. Click Next.

On the Review Hardware Mapping screen, click Next.

On the Review Memory Map screen, to view the memory map, click View/Edit. Click Next.

On the Validate Model screen, to check the compatibility of the model for implementation, click Validate. Click Next.

On the Build Model screen, to build the model, click Build. An external shell opens when FPGA synthesis begins. Click Next.

On the Connect Hardware screen, to test the connectivity of the host computer with the SoC board, click Test Connection. To go to the Run Application screen, click Next.

The FPGA synthesis often takes more than 30 minutes to complete. To save time, you can use the provided pregenerated bitstream by following these steps.

Close the external shell to terminate synthesis.

Copy the pregenerated bitstream to your project folder by entering this command at the MATLAB command prompt.

copyfile(fullfile(matlabshared.supportpkg.getSupportPackageRoot, ... 'toolbox','soc','supportpackages','xilinxsoc', ... 'xilinxsocexamples','bitstreams', ... 'soc_rfsoc_datacapture-XilinxZynqUltraScale_RFSoCZCU111EvaluationKit.bit'),'./soc_prj');

Load the pregenerated bitstream and run the model on the SoC board by clicking Load and Run.

After the bit file is loaded, open the generated software model, copy the spectrum analyzer and scope from the top model and connect to the rate transition block as shown in this figure, and run the model. You can observe the tone frequency of the ADC channel 1 default in the spectrum analyzer.

Run the model in external mode and verify that the received tone is at 0.5 MHz on the Spectrum Analyzer. By default, ADC channel 1 is configured for visualization. To select a different ADC channel, modify the adcChannelSelect value. The tone signal as transmitted through various DAC channels is scaled differently. This is seen as the difference in the peak value for the received tone in the spectrum scope. For instance, running the model with adcChannelSelect value 5 (corresponding to Channel 5) results in a lower peak on the Spectrum Analyzer when compared with Channel 1.

Note: You do not see any output in Channel 3 and Channel 4 on the XM500 balun card. These channels support 1 to 4 GHz range, which is above the transmitted tone of 0.5 MHz.

Implement and Run on DFE ZCU670 Hardware

Connect the XM755 balun card and complete the loopback between the DACs and ADCs as shown in table.

To implement the soc_rfsoc_datacapture model on a supported SoC board, use the SoC Builder tool. Ensure that the Hardware Board option is set to Xilinx Zynq UltraScale+ RFSoC DFE ZCU670 Evaluation Kit on the System on Chip tab of the Simulink toolstrip. Set the same board in the soc_rfsoc_datacapture_proc processor model and follow the same SoC Builder steps defined in the above section. Load the generated bitstream onto the hardware.

Run the software model in external mode and verify that the received tone is at 0.5 MHz on the Spectrum Analyzer.

Implement and Run on ZCU216 Hardware

Connect the XM655 balun card and complete the loopback between the DACs and ADCs as shown in table.

To implement the soc_rfsoc_IQ_datacapture_top model on a supported SoC board, use the SoC Builder tool. Ensure that the Hardware Board option is set to Xilinx Zynq UltraScale+ RFSoC ZCU216 Evaluation Kit on the System on Chip tab of the Simulink toolstrip, and follow the same SoC Builder steps defined in the above section. However, to load the pregenerated bitstream, use the below command for the ZCU216 evaluation kit.

copyfile(fullfile(matlabshared.supportpkg.getSupportPackageRoot,'toolbox','soc','supportpackages','xilinxsoc','xilinxsocexamples','bitstreams','soc_rfsoc_IQ_datacapture_top-XilinxZynqUltraScale_RFSoCZCU216EvaluationKit.bit'),'./soc_prj');

Run the software model in external mode and verify that the received tone is at 0.5 MHz on the Spectrum Analyzer.

Implement and Run on ZCU208 Hardware

Connect the XM655 balun card and complete the loopback between the DACs and ADCs as shown in table.

To implement the soc_IQ_datacapture_top model on a supported SoC board, use the SoC Builder tool. Ensure that the Hardware Board option is set to Xilinx Zynq UltraScale+ RFSoC ZCU208 Evaluation Kit on the System on Chip tab of the Simulink toolstrip, and follow the same SoC Builder steps defined in the above section. However, to load the pregenerated bitstream, use the below command for the ZCU208 evaluation kit.

copyfile(fullfile(matlabshared.supportpkg.getSupportPackageRoot,'toolbox','soc','supportpackages','xilinxsoc','xilinxsocexamples','bitstreams','soc_IQ_datacapture_top-XilinxZynqUltraScale_RFSoCZCU208EvaluationKit.bit'),'./soc_prj');

Run the software model in external mode and verify that the received tone is at 15 MHz on the Spectrum Analyzer.

Profiling Results

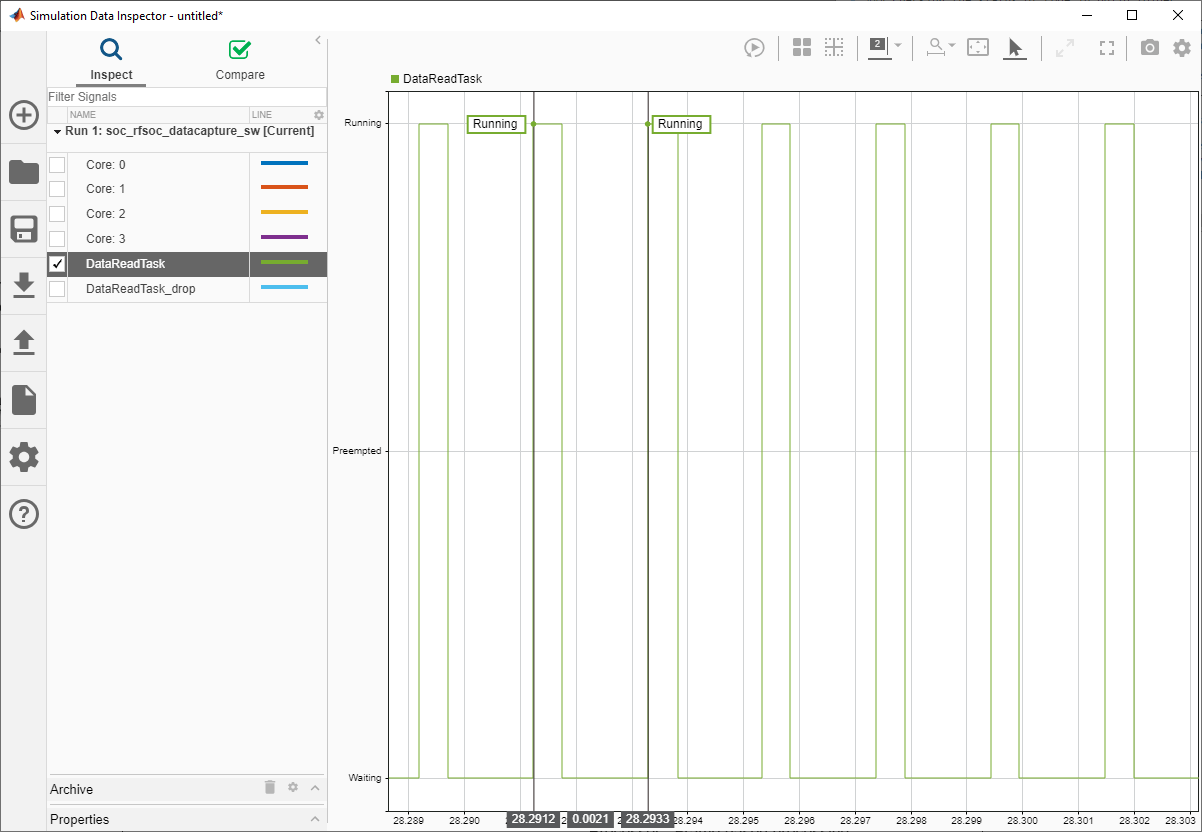

You can profile the execution of processor task durations using on-device profiling features of SoC Blockset. This tool is useful to debug and verify that the tasks are completed in a timely manner with the data received asynchronously from the FPGA.

To enable the processor task profiling, open the Configuration Parameter dialog box in generated software model and select Hardware Implementation > Hardware Board settings > Task Profiling on processor. Select Show on SDI and then select Save to file.

Set Instrumentation to Code. Set the simulation stop time to 10 seconds and run the model in the external mode. After simulation is completed, open the Simulation Data Inspector (SDI), navigate to the latest run, and add a signal DataReadTask to the plot. From the plot you can observe the frame rate as 2 milliseconds.

Summary

This example demonstrated how to implement a wireless design by including the RF Data Converter on the Xilinx RFSoC device. Using SoC Builder, you implemented a system that generated a tone from the FPGA and performed the loopback through the RF Data Converter block. You verified that the system worked as expected on the hardware.