Xilinx FPGA and SoC Devices

HDL Coder™ can generate an IP core, integrate it into your Vivado® project, and program the Xilinx hardware. To deploy your design to the Xilinx hardware, you must install the HDL Coder Support Package for Xilinx FPGA and SoC Devices. For installation information, see HDL Coder Supported Hardware.

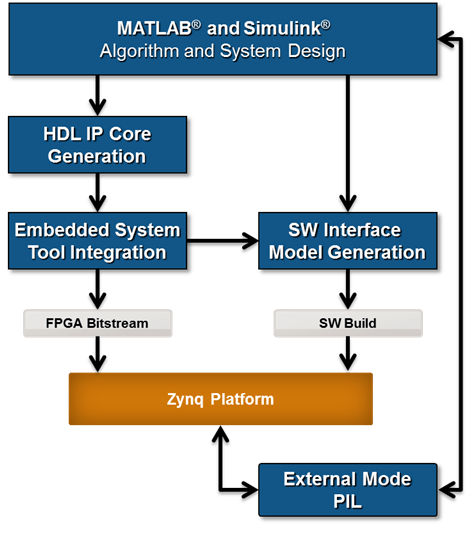

HDL Coder Support Package for Xilinx FPGA and SoC Devices supports the generation of IP cores that can be integrated into FPGA designs using Xilinx Vivado. When used in combination with Embedded Coder®, this solution can program the Xilinx Zynq® SoC using C and HDL code generation. The hardware-software co-design workflow spans simulation, prototyping, verification, and implementation. Using Embedded Coder, you can generate and build the embedded software, and run it on the ARM® processor. See Hardware-Software Co-Design Workflow for SoC Platforms.

| Device Family | Board | Available Reference Designs |

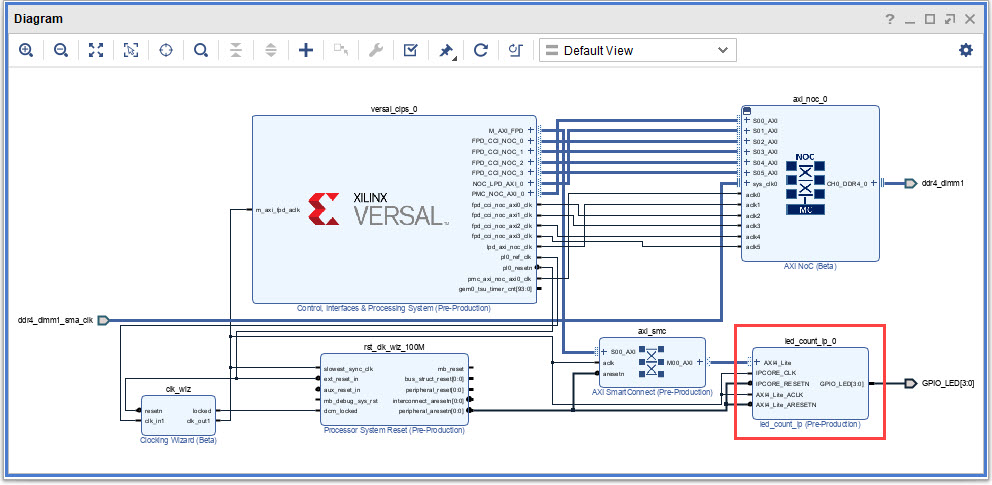

Versal® | Xilinx Versal AI Core Series VCK190 evaluation kit | |

Zynq UltraScale+™ RFSoC | Xilinx Zynq UltraScale+ RFSoC ZCU111 evaluation kit | Default System with AXI4 Stream Interface |

Xilinx Zynq UltraScale+ RFSoC ZCU216 evaluation kit | ||

Zynq UltraScale+ MPSoC | Xilinx Zynq UltraScale+ MPSoC ZCU102 evaluation kit | |

Zynq | Xilinx Zynq ZC706 evaluation kit | Default System with AXI4 Stream Interface |

Xilinx Zynq ZC702 evaluation kit | ||

ZedBoard™ | ||

Kintex®-7 | Xilinx Kintex-7 KC705 development board | |

Virtex®-7 | Xilinx Virtex-7 VC707 development board | |

Artix®-7 | Xilinx Artix-7 35T Arty development board |

Note

To extend support to new hardware, see Create a Custom Hardware Platform.

For more information on tool and board support, see Supported EDA Tools and Hardware.

Categories

- Setup and Configuration

Download and install support package for use with third-party EDA tools and supported hardware

- Get Started With Hardware-Software Co-Design

Deploy generated HDL code on a target hardware platform

- Generate an IP Core and Bitstream

Generate HDL IP core and bitstream that contain HDL code for deployment on standalone Xilinx FPGA boards and SoC Devices

- Target Xilinx RFSoC Hardware

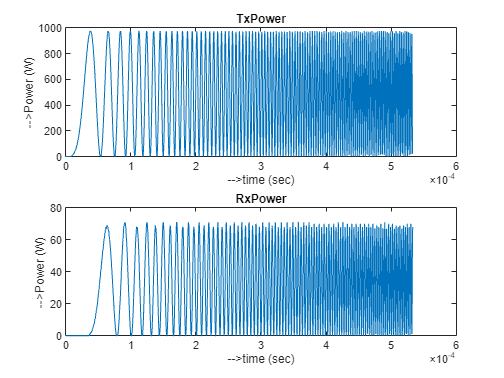

Run your MATLAB® or Simulink® algorithm on the Xilinx RFSoC target hardware