Model Design Using Data Valid Interfaces

Guideline ID

1.6.1

Severity

Informative

Description

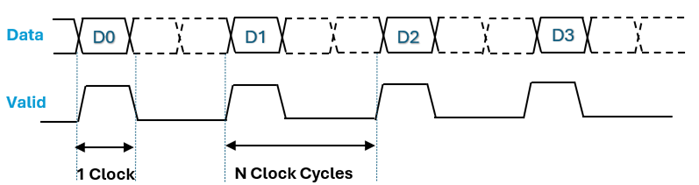

In hardware designs, data streams often contain gaps between samples. You can use a data valid signal to indicate whether a data sample is valid for processing. This guideline describes recommended practices for modeling data valid interfaces in Simulink® for HDL‑targeted designs.

Model Data with Regular Gaps

If your model has data streams where the samples arrive periodically, you can use either multi‑rate or single‑rate techniques, depending on the data characteristics.

Continuous data streams with an effective sample rate equal to a fraction of the clock rate (1/N of the clock rate) can be modeled using a multi‑rate model. For more information on multirate modeling, see Code Generation from Multirate Models.

Alternatively, you can represent the same behavior in a single‑rate model by using a data valid signal that asserts once every N clock cycles.

Using a data valid signal in a single-rate model allows you to control the data flow and makes the model compatible with the data valid interfaces that the IP blocks in DSP System Toolbox™, Vision HDL Toolbox™, and Wireless HDL Toolbox™ use.

You can also use data valid interfaces to reuse hardware resources. When the valid signal asserts only once every N clock cycles, a single hardware resource can operate across multiple cycles.

For example, when sharing multipliers in a filter design, the valid signal ensures that the resource processes new input data only when the data is valid. In DSP HDL Toolbox™ FIR blocks, you can control this behavior using the Minimum number of cycles between valid input samples parameter. Ensure that the input data does not change faster than the specified cycle spacing.

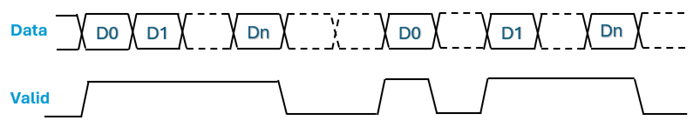

Model Data with Irregular Gaps

If your model contains a data stream that has irregular or nonperiodic gaps, then you must design a single-rate model that has a data valid signal. Models that have irregular or nonperiodic gaps in their data streams include:

Models with input data that is continuous during normal operation, but pauses during configuration.

Frame-based models that produce output data in bursts

Do not use multirate models for applications that have irregular or nonperiodic gaps. Multirate models cannot capture the irregular gap patterns effectively.

Match Pipeline Registers in Data and Valid Paths

If your model contains pipeline registers, you must model the data valid signals together. To align the valid signal with its corresponding data sample, add matching latency to the valid path whenever you introduce latency in the data path.

Enable Delay Balancing so that when HDL Coder inserts pipeline registers automatically through optimization features, it also inserts matching registers in the valid path. For more information, see Understand Delay Balancing in HDL Coder.

See Also

Enabled Synchronous Subsystem | Unit Delay Enabled Synchronous