Model Design for Frame-Based IP Core Generation

You can use the frame-to-sample optimization to generate IP cores for frame-based models. The frame-to-sample optimization maps matrices and vectors to the AXI4-Stream ports and matrices to AXI4-Stream Video interfaces, and then creates the necessary logic to handle the streamed data in the frame-based design.

Frame-Based Modeling for AXI4-Stream Interfaces

If your model includes streamed data, but does not process videos, you can use the frame-to-sample optimization to generate an IP core that operates on frames of data, then map the data ports to the streaming interface. You can then translate and implement your frame-based models on pixel-based hardware. See HDL Code Generation from Frame-Based Algorithms.

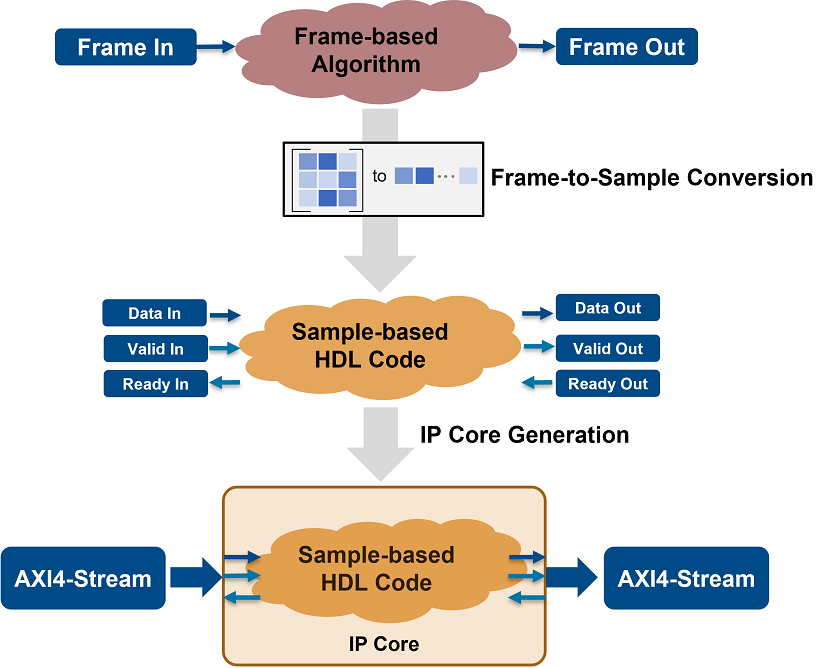

When you generate the IP core, you map the frame data ports at the DUT boundary to AXI4-Stream interfaces. HDL Coder™ generates the Valid and Ready signals for each port. This image shows a top-level overview of the frame-to-sample optimization and IP core generation.

Map vectors, complex vectors, matrices, and complex matrix data to AXI4-Stream interfaces by using frame-to-sample conversion optimization. The TLAST signal is created in the generated IP core and the signal is asserted when the number of valid samples counts to the frame size of the data port.

For an example on modeling a frame-based model with AXI4-Stream interfaces, see Generate IP Core for Frame-Based Model with AXI4 Stream Interfaces.

To model your algorithm using a simplified streaming protocol and a sample-based DUT, see Model Design for AXI4-Stream Interface Generation.

Frame-Based Modeling for AXI4-Stream Video Interfaces

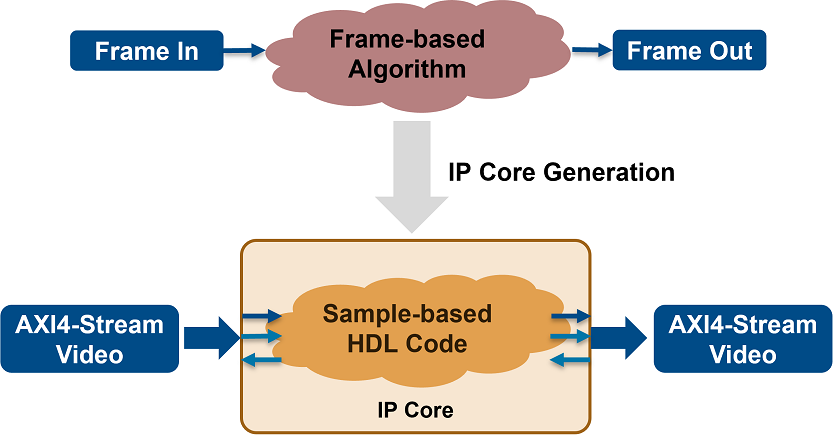

If your model includes streamed video ports, you can use the frame-to-sample optimization to map the two-dimensional matrix ports of your DUT to an AXI4-Stream Video interface. You can then prototype your algorithm in Simulink® using frame-based modeling and test the functionality on live video inputs and outputs.

When you use the frame-to-sample optimization, HDL Coder:

Converts the interface and generates the Data, Valid, and Ready signals for each port.

Inserts the video porch and handles the start of frame (SOF) signal.

This image shows a top-level overview of the frame-to-sample optimization and IP core generation.

Map matrix ports to an AXI4-Stream Video interface by using the frame-to-sample optimization. The TUSER and TLAST signals are created during IP core generation. TUSER is asserted at the start of every frame and TLAST is asserted at the end of each line.

Video Porch Insertion Logic

Video capture systems scan video signals from left to right and from top to bottom. As these systems scan, they generate inactive intervals between lines and frames of active video. This inactive interval is called a video porch. When you generate an IP core using frame-to-sample conversion, the active pixels per line and the active lines in each frame are defined by the frame size of the frame-based model and they are not configurable at runtime. However, you can configure the horizontal and vertical porch. HDL Coder inserts vertical and horizontal porch to the pixel stream based on the AXI4-Lite registers in the generated IP core. You can customize these porch parameters for each video frame:

Horizontal porch length (Default: 280)

Vertical porch length (Default: 45)

The default values correspond to the porch values of a 1080p video frame.

This figure shows a video frame with the horizontal porch split into a front and a back porch.

![]()

To model your algorithm using a sample-based DUT and the streaming pixel protocol, see Model Design for AXI4-Stream Video Interface Generation.

For an example on modeling a frame-based model with AXI4-Stream Video interfaces, see Generate IP Core from Frame-Based Model with AXI4 Stream Video Interface.

Enable the Optimization

To use the frame-to-sample optimization:

Enable the frame-to-sample optimization. See, Enable frame to sample conversion.

Enable frame-to-sample optimization on the input data signal on the DUT that maps to the AXI4 Stream or AXI4-Stream Video interfaces.

Stream Multiple Samples per Cycle

Since R2025a

To stream multiple samples per cycle, set the Samples per cycle parameter to a value greater than one. When you specify more than one sample per cycle, HDL Coder packs the samples together and streams them in a single clock cycle. All streamed ports use the same value for Samples per cycle.

When your streamed ports are non-complex ports, you can set the Packing

Mode parameter in the HDL Workflow Advisor to Bit

Aligned or Power of 2 Aligned. For more

information on packing modes, see Packing Mode.

When you enable host script generation as part of the IP core generation, you can

specify the SamplePackingFactor and

SampleAlignment name-value arguments to the addAXI4StreamInterface function. The

SampleAlignment parameter sets the value of the

Packing Mode parameter for the streamed port.

Offload a Single Large Delay from Frame-Based Models to External Memory

Since R2023a

To map large integer delays to input and output DUT ports, use the Delay size threshold for external memory (kilobytes) parameter. This parameter specifies a threshold size in kilobytes for external memory, to map large integer delays to input and output DUT ports.

To generate an IP core for a model with a single delay when you enable frame-to-sample conversion, map the streamed inputs and outputs of your DUT to an AXI4-Stream or AXI4-Stream Video interface. Set the Delay size threshold for external memory (kilobytes) parameter and use a reference design or a generic platform that provides at least one AXI4-Master interface. HDL Coder maps the external delay ports to external memory, generates frame management logic, and AXI4-Master based read and write controllers to store the delays.

Offload Multiple Large Delays from Frame-Based Models to External Memory

Since R2026a

When you enable frame-to-sample conversion, offload multiple large delays to external memory by mapping the streamed inputs and outputs of your DUT to an AXI4-Stream or AXI4-Stream Video interface. Use the Offload large delays to external memory using parameter in the Interface Settings tab of the IP Core Editor to choose between using a single shared AXI4-Master interface or separate individual AXI4-Master interfaces for each delay. Choose a reference design or a generic platform that provides the required AXI4-Master interfaces based on your Offload large delays to external memory using parameter setting. HDL Coder enables efficient use of external memory by generating a frame manager that converts the streaming protocol to a burst transfer optimized memory protocol.

Modeling Requirements

Model only the Data signals. The frame-to-sample conversion optimization generates the Ready and Valid signals.

When you have multiple samples per cycle and both master and slave channels, the packing mode for both channels must be the same.

When you stream multiple samples per cycle, you must set the Scalarize ports configuration set option to

dutlevel.When your streamed ports are complex ports you can set the Packing Mode parameter to

Power of 2 Alignedonly.3D ports are not supported for IP core generation.

You cannot stream multiple samples per cycle when you use an AXI4-Stream Video interface.

When you offload large delays to external memory, these limitations apply:

- HDL Coder

maps only FIFO blocks generated as delays during code generation to external memory. You cannot move outside the DUT or map to external memory, delay blocks created by pipeline optimizations in the generated model and code.

In IP core generation, to map frame delays to external memory streamed ports must be non-complex vectors or 2-D matrices and the Samples per cycle parameter must be set to

1.If you have more than one delay in your MATLAB® design, you cannot use the Offload large delays to external memory using parameter in the MATLAB to HDL Workflow Advisor. You must use a shared AXI4-Master interface for the delays.

If you set the Offload large delays to external memory using parameter to

Independent interfaces, the reference design must have at least the same number of interfaces as the number of delays in your design. HDL Coder does not generate the AXI4-Master interfaces.

See Also

Topics

- Model Design for AXI4-Stream Interface Generation

- Streaming Pixel Interface (Vision HDL Toolbox)

- HDL Code Generation from Frame-Based Algorithms