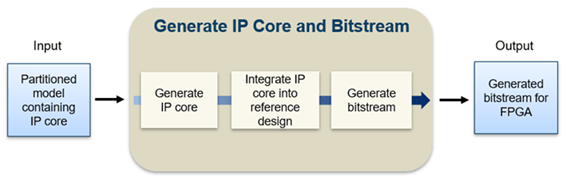

Generate IP Core and Bitstream

The IP core is a shareable and reusable HDL component that implements a specific function, typically an algorithm. An IP core consists of IP core definition files, HDL code generated for your algorithm, a C header file containing the register address map, and the IP core report.

By using the IP Core Generation workflow in the HDL Workflow Advisor,

HDL Coder™ can generate an IP core that contains the HDL source code and the C header

files for integrating the IP core into your Vivado®, Qsys or Libero® project, and then program the target hardware. You can integrate the IP core

into a default or custom reference design depending on the target platform, and generate a

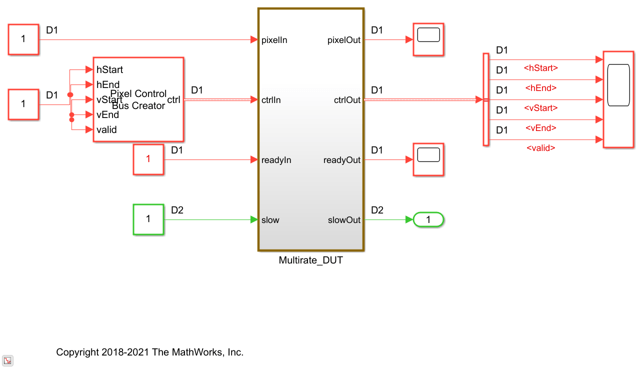

bitstream to be deployed to your FPGA hardware. The input is a designed IP core in a

Simulink® model or MATLAB® function. The output is a bitstream generated by HDL Coder from the IP core.

For more details on the workflow, see Targeting FPGA & SoC Hardware Overview.

Classes

hdlcoder.WorkflowConfig | Configure HDL code generation and deployment workflows |

Topics

IP Core Generation

- Custom IP Core Generation

Generate a custom IP core from a model or algorithm using the HDL Workflow Advisor. - Custom IP Core Report

You generate an HTML custom IP core report by default when you generate a custom IP core. - Generate Board-Independent HDL IP Core from Simulink Model

When you open the HDL Workflow Advisor and run theIP Core Generationworkflow for your Simulink model, you can specify a generic Xilinx platform, a generic Intel platform, generic Microchip platform or generic platform. - Generate Board-Independent IP Core from MATLAB Algorithm

Board-independent IP core generation from MATLAB. - Generate HDL IP Core with Multiple AXI4-Stream and AXI4 Master Interfaces

Learn how you can map your DUT ports to multiple AXI4-Stream, AXI4-Stream Video, and AXI4 Master interfaces. - IP Core Reset Interface

Learn how HDL Coder automatically inserts logic to synchronize global reset signal to IP core clock domain. - IP Core Generation Workflow for Standalone FPGA Devices

Learn how to use the IP Core Generation workflow with standalone FPGA devices and embed the IP core into the reference design. - Generate Board-Independent HDL IP Core for Xilinx Platforms

Integrate generated IP core into a Xilinx Vivado project. (Since R2024b)

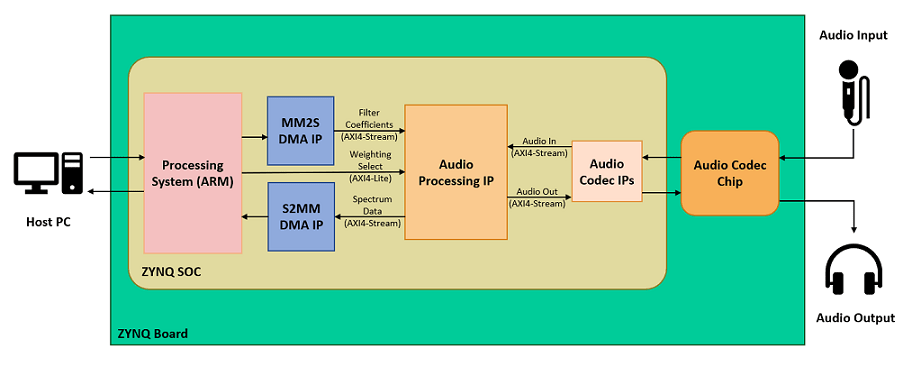

Xilinx Zynq Reference Designs

- Default System Reference Design for AMD SoC Device

Learn about the default system reference design for AMD® SoC device and using the reference design. - Default System with AXI4-Stream Interface Reference Design

Learn about how to use the default system with AXI4-Stream Interface reference design and its requirements. - Default Video System Reference Design

Learn about the default video system reference design and its requirements. - Default System with External DDR Memory Access Reference Design

Learn about the default system with external DDR3, DDR4, LPDDR4 and shared memory access reference design and its requirements.

Intel SoC Reference Designs

- Default System Reference Design for Intel SoC Devices

Learn about the default system reference design and using the reference design for Intel SoC Devices. - Default System with External DDR4 Memory Access Reference Design

Learn about the default system with external DDR3 memory access reference design and its requirements.

Microchip SoC Reference Designs

- Default System Reference Design

Learn about the default system reference design and using the reference design.

Reference Design Integration

- IP Caching for Faster Reference Design Synthesis

Use IP caching to speed up reference design synthesis time by using an out-of-context workflow. - Resolve Timing Failures in IP Core Generation and Simulink Real-Time FPGA I/O Workflows

Resolve timing failures in Build FPGA Bitstream step of IP Core Generation Workflow or Simulink Real-Time FPGA I/O Workflow for Vivado-Based Boards.