Code Optimization for HVX

Generate optimized code for digital signal processing from blocks, System objects, and math operators using code replacement.

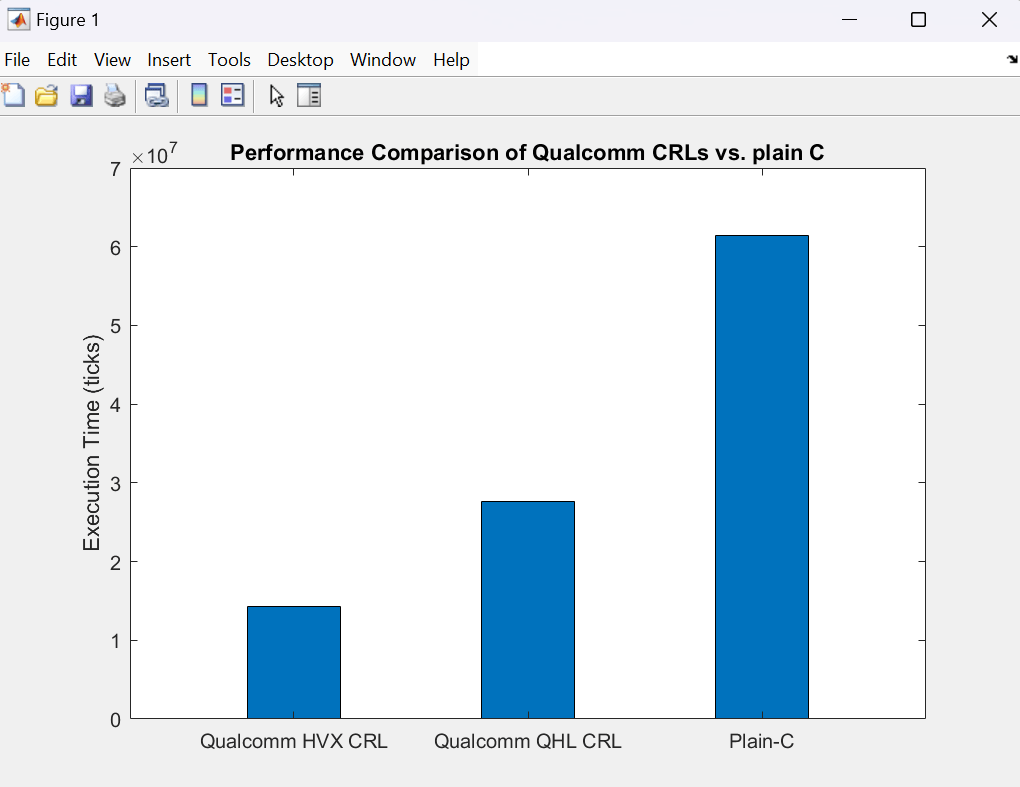

Qualcomm® Hexagon® processors require specific conditions to allow code replacement with the Hexagon Vector eXtension (HVX) for vector processors. You use this code replacement when generating C/C++ code from a model.

Blocks

| HVX Conv2D | 2-D convolution for HVX (Since R2026a) |

| HVX Dilate | 2-D grayscale dilation for HVX (Since R2026a) |

| HVX Erode | 2-D grayscale erosion for HVX (Since R2026a) |

Functions

QHVXIPCV.conv2D | 2-D convolution for HVX (Since R2026a) |

QHVXIPCV.dilate3x3 | 2-D grayscale dilation with a 3-by-3 square structuring element for HVX (Since R2026a) |

QHVXIPCV.dilate5x5 | 2-D grayscale dilation with a 5-by-5 square structuring element for HVX (Since R2026a) |

QHVXIPCV.dilate7x7 | 2-D grayscale dilation with a 7-by-7 square structuring element for HVX (Since R2026a) |

QHVXIPCV.erode3x3 | 2-D grayscale erosion with a 3-by-3 square structuring element for HVX (Since R2026a) |

QHVXIPCV.erode5x5 | 2-D grayscale erosion with a 5-by-5 square structuring element for HVX (Since R2026a) |

QHVXIPCV.erode7x7 | 2-D grayscale erosion with a 7-by-7 square structuring element for HVX (Since R2026a) |

Topics

- Conditions for Code Replacement of DSP Blocks with HVX

Specify conditions for DSP blocks to allow code replacement with the Hexagon Vector Extension.

- Conditions for Code Replacement of DSP System Objects with HVX

Specify conditions for DSP System objects to allow code replacement with the Hexagon Vector Extension.

- Conditions for Code Replacement of Math Operators with HVX

Specific CRL conditions for math operators to allow code replacement with the Hexagon Vector Extension.

- Generate SIMD Code using Hexagon and HVX Instruction Set for Qualcomm Hexagon Processors

Learn how to generate SIMD code from MATLAB® functions using Hexagon and HVX instruction set for Qualcomm Hexagon processors. (Since R2026a)